## YOKOHAMA NATIONAL UNIVERSITY

## DOCTOR'S THESIS

## Research on qubit control and readout systems using superconductor and cryo-CMOS circuits (超伝導回路と低温CMOSを用いた量子 ビット制御・読出し回路の研究)

Author: Hongxiang SHEN Supervisor: Prof. Nobuyuki YOSHIKAWA

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Engineering

in the

Department of Mathematics, Physics, Electrical Engineering and Computer Science Graduate school of engineering science

February 2, 2023

#### YOKOHAMA NATIONAL UNIVERSITY

## Abstract

Department of Mathematics, Physics, Electrical Engineering and Computer Science

Doctor of Engineering

# Research on qubit control and readout systems using superconductor and cryo-CMOS circuits (CMOS)

by Hongxiang SHEN

Nowadays, semiconductor technology has developed at a rapid pace because of high integration and stable performance. Moore's law even has been confirmed that the number of transistors in a dense integrated circuit (IC) doubles about every two years. Traditional computer become smaller and faster. However, with the reduction in size of transistors, Moore's law seems to be broken down soon. Besides, the problem of power consumption should be paid attention caused mainly by accumulation of data in the future. For low power consumption society, people start to focus on the superconducting circuits which owns the potential to relieve this problem. On the other hand, quantum computers appear to be capable, at least in principle, of solving certain problems far faster than any conceivable classical computer. This may reveals a new way to achieve quantum computer using superconductor circuits where both of them works within cryogenic temperature.

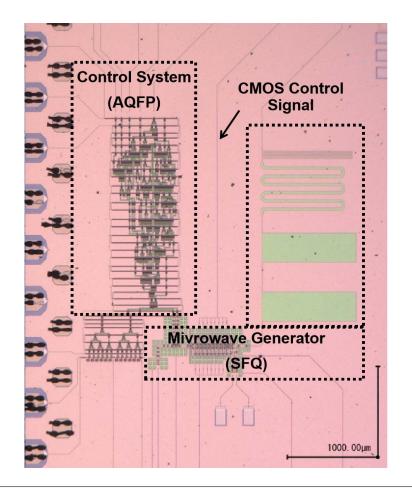

In this thesis we introduce the research process on quantum bit control and readout system using cryogenic circuits. We suggest a feed back schematic within the cryogenic temperature so that it save lots of cables. THe schematic contains the SFQ,AQFP,and Cryogenic CMOS circuits. Microwave generator as core part designed with SFQ is applied to control qubit. AQFP and cryogenic CMOS circuits is applied to control the generator. The measurement result confirm this circuits operation. Detail data of each circuits is in each chapters. Besides, we present suggestion to improve the characteristic of microwave generator. The SNR is higher than before and initial phase of microwave is controllable. It has been shown that quantum error correction (QEC) can be realized with cryogenic temperature, where it enables the possibility of performing fault-tolerant quantum computing in future.

## Acknowledgements

This thesis resulted from my study at Yoshikawa laboratory, I'd like to express my appreciation to everyone who has supported me during my doctor studies in Japan. My advisor Professor Nobuyuki Yoshikawa is who I want to thank the most. Due to my original major is not superconducting circuits, he help me a lot with great patience during my student period. It is his patience and kindness that give me confidence and courage to overcome the bottleneck on the research. Moreover, he provide the chance to attend the many projects, such as qubit controlling and cold flux where I can learn lot knowledge. Besides, I'd like to thank Prof. Yuki Yamanashi. He give me lots suggestions on my research. I'd like to thank Prof. Naoki Takeuchi that I learned a researcher should have a rigorous attitude. I'd like to thank Dr. Hideo Suzuki that I obtained the help and suggestion both in my life and study. I wish to thank the prof.Yuxing He who teach me the designed method of RF circuits. I'd like to thank the prof.Christopher Ayala and prof.Olivia Chen who provide me the chance to learn more about design tools of synopsy.

Expect for the professors, I want to express my gratitude to the students in the Yoshikawa laboratory and yamanashi laboratory. The past member of QC group, such as Shiori Michibayashi and Yoshihiro Takagawa, they do lots of previous research about qubit controlling system. What's more, current group member Shu Sasaki and Nagamatsu Yoshiaki do lots of improvement which brings us closer to achieve quantum computer. Thanks to the unremitting efforts of my QC members, I can achieve my present achievement. I'd like to thank Yuki Hironaka, Taiki Yamae and Tomoyuki Tanaka that they help me in my research and daily life.

Finally, I would like to thank my parents for their full support for my study in Japan.

## Contents

| Abstract |                   |         |                                             |               |  |  |

|----------|-------------------|---------|---------------------------------------------|---------------|--|--|

| A        | cknow             | wledge  | ments                                       | ii            |  |  |

| 1        | <b>Bac</b><br>1.1 | kgroun  | ı <mark>d</mark><br>luction                 | <b>1</b><br>1 |  |  |

|          |                   |         |                                             |               |  |  |

|          | 1.2<br>1.3        |         | rements For Quantum Computing               |               |  |  |

|          |                   |         | For Fault-Tolerant Computer                 | 5             |  |  |

|          | 1.4               | Kesea   | rc Purpose                                  | 5             |  |  |

| 2        | Mic               |         | e Generator Using SFQ                       | 7             |  |  |

|          | 2.1               |         | hson Junction                               | 7             |  |  |

|          | 2.2               | Signle  | e Flux Quantum Logic Circuits               | 9             |  |  |

|          | 2.3               | SFQ L   | Logic Gate                                  | 11            |  |  |

|          |                   | 2.3.1   | Josephson Transmission Line (JTL)           | 11            |  |  |

|          |                   | 2.3.2   | Confluence Buffer (CB)                      | 12            |  |  |

|          |                   | 2.3.3   | T-Flip Flop (TFF)                           | 13            |  |  |

|          |                   | 2.3.4   | Non Destructive Read Out (NDRO)             |               |  |  |

|          |                   | 2.3.5   | DC/SFQ Converter (DSC)                      |               |  |  |

|          | 2.4               | Qubit   | Control                                     | 16            |  |  |

|          |                   | 2.4.1   | Flux-Tunable Transmon Qubit                 | 16            |  |  |

|          |                   | 2.4.2   | Control of Transmon Qubit                   |               |  |  |

|          |                   | 2.4.3   | Filter Response of Pulse Signal             |               |  |  |

|          |                   | 2.4.4   | Delay Generator (DG)                        |               |  |  |

|          | 2.5               |         | wave Generator With Pair Pulses             | 25            |  |  |

|          |                   | 2.5.1   | Microwave Generator                         |               |  |  |

|          |                   | 2.5.2   | Photo and Parameter of Fabricated Circuits  | 27            |  |  |

|          |                   | 2.5.3   | Function Verification Under Low Speed       | 28            |  |  |

|          |                   | 2.5.4   | Measurement Under High Speed                |               |  |  |

|          |                   |         | Duration Measurement Under High Speed       |               |  |  |

|          |                   |         | Amplitude Measurement Under High Speed      |               |  |  |

|          | 2.6               | Concl   | usion                                       |               |  |  |

| 3        | Tim               | in a Ca | ntroller Circuits And Integrator Using AQFP | 37            |  |  |

| 3        | 3.1               |         | patic Quantum Flux Parametron (AQFP)        | 37            |  |  |

|          | 5.1               | 3.1.1   |                                             | 37            |  |  |

|          |                   |         | Structure of AQFP         4 Phase Operation |               |  |  |

|          |                   | 3.1.2   | 4-Phase Operation                           | 40            |  |  |

|          | 2.2               | 3.1.3   | AQFP Logic Cells                            | 41            |  |  |

|          | 3.2               | Iimin   | g Control Circuits With AQFP                |               |  |  |

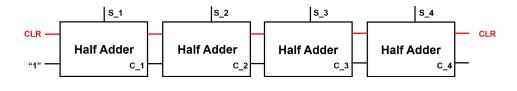

|          |                   |         | Counter (4bits)                             | 46            |  |  |

|   |                                                        | Register                                              | 48 |  |  |  |  |

|---|--------------------------------------------------------|-------------------------------------------------------|----|--|--|--|--|

|   |                                                        | AQFP to SFQ Interface                                 | 49 |  |  |  |  |

|   |                                                        | Simulation                                            | 50 |  |  |  |  |

|   |                                                        | Chip Fabrication and Measurement result               | 50 |  |  |  |  |

|   | 3.3                                                    | 8-bit Integrator Circuits Using AQFP                  | 54 |  |  |  |  |

|   |                                                        | 3.3.1 Grey Zone of AQFP                               | 55 |  |  |  |  |

|   |                                                        | 3.3.2 Integration Theory                              | 58 |  |  |  |  |

|   |                                                        | 3.3.3 AQFP Integrator Circuits                        | 60 |  |  |  |  |

|   |                                                        | 3.3.4 Chip Fabrication and Measurement Result         | 61 |  |  |  |  |

|   | 3.4                                                    | Conclusion                                            | 63 |  |  |  |  |

| 4 | Arbitrary Envelope Signal Generator Using Cryo-CMOS 64 |                                                       |    |  |  |  |  |

|   | 4.1                                                    | Device of NMOS and PMOS                               | 64 |  |  |  |  |

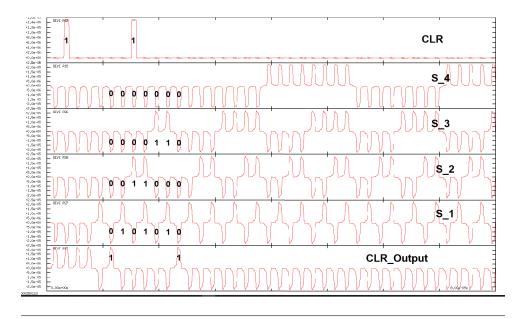

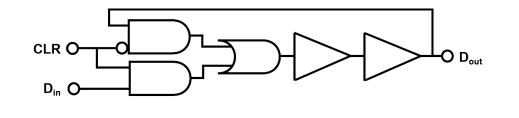

|   |                                                        | 4.1.1 Digital Cell Designed Using CMOS                | 66 |  |  |  |  |

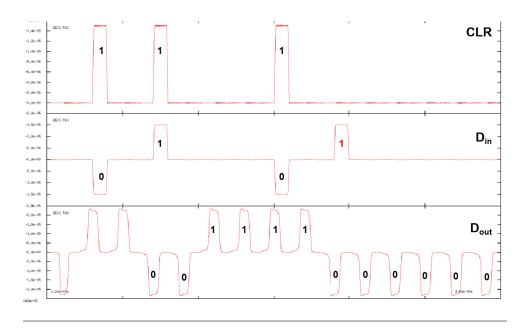

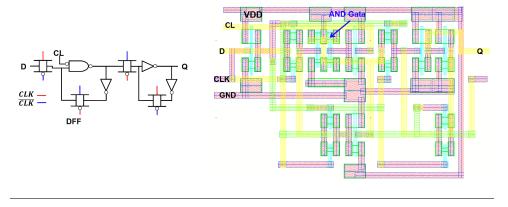

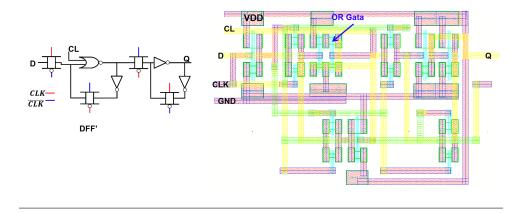

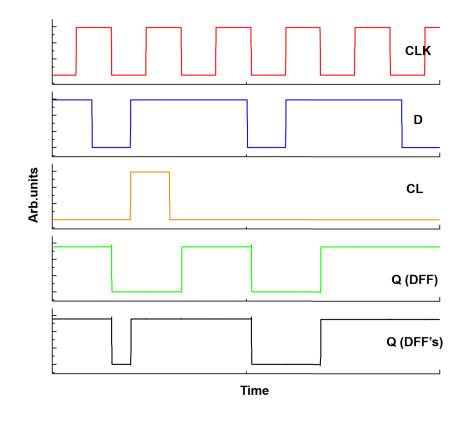

|   |                                                        | 4.1.2 D Filp-Flop                                     | 68 |  |  |  |  |

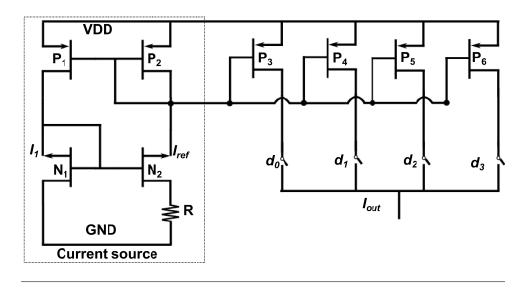

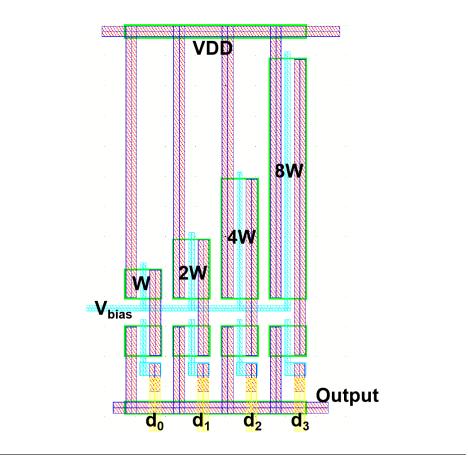

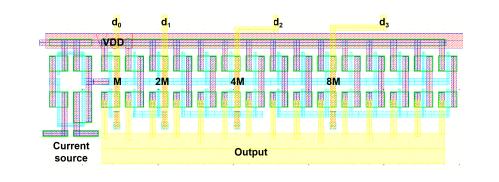

|   |                                                        | 4.1.3 Digital to Analog Converter                     | 70 |  |  |  |  |

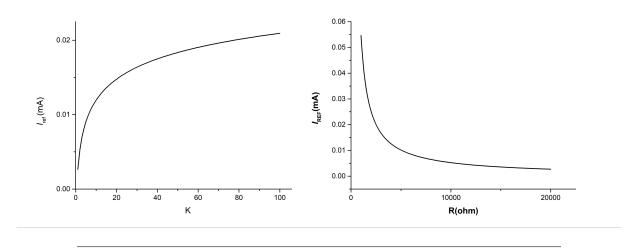

|   |                                                        | Theory                                                | 70 |  |  |  |  |

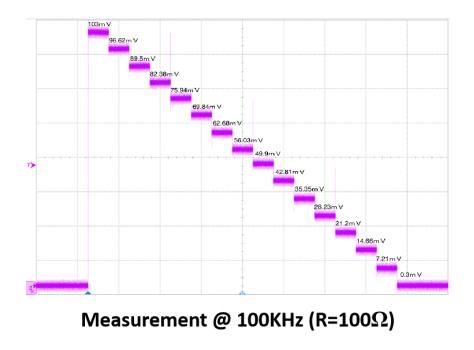

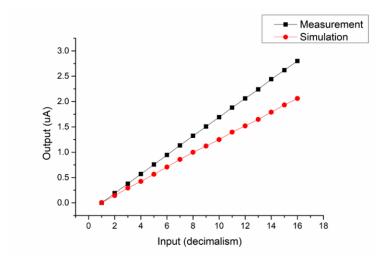

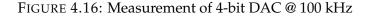

|   |                                                        | Measurement                                           | 73 |  |  |  |  |

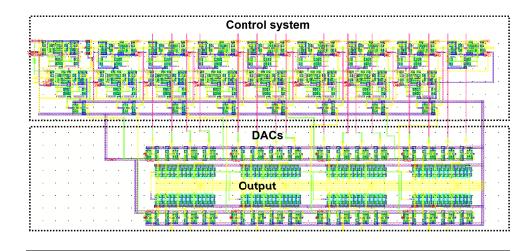

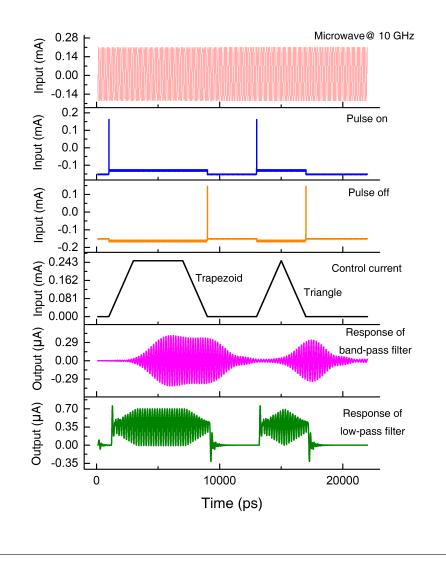

|   | 4.2                                                    | Arbitrary Envelope Signal Generator                   | 74 |  |  |  |  |

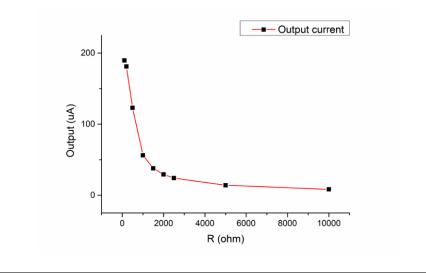

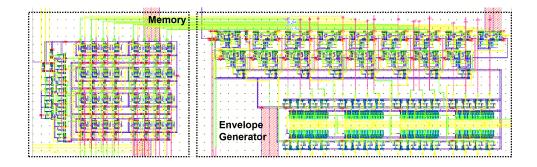

|   |                                                        | 4.2.1 Structure of System                             | 74 |  |  |  |  |

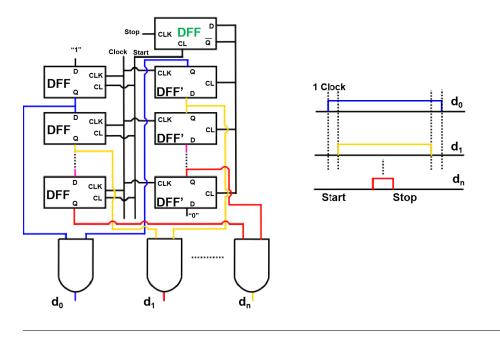

|   |                                                        | Control System                                        | 75 |  |  |  |  |

|   |                                                        | Low Pass Filter                                       | 76 |  |  |  |  |

|   |                                                        | 4.2.2 Measurement (Without Filter)                    | 77 |  |  |  |  |

|   | 4.3                                                    | Conclusion                                            | 80 |  |  |  |  |

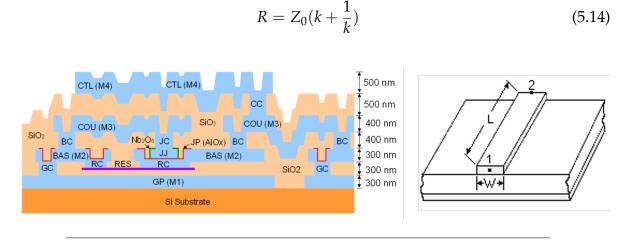

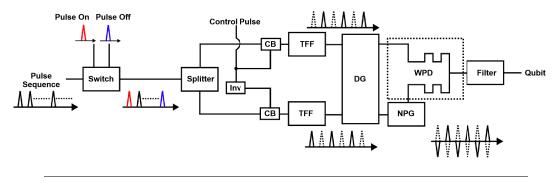

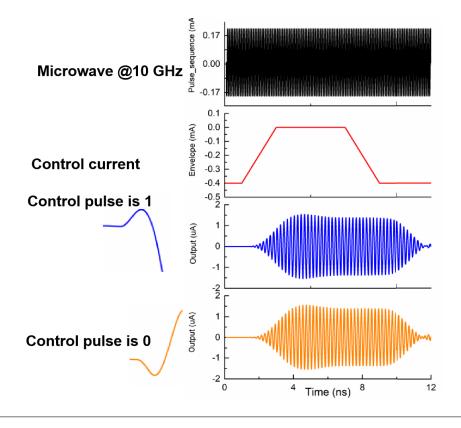

| 5 | Imp                                                    | Improvement for Microwave Generator                   |    |  |  |  |  |

|   | 5.1                                                    |                                                       | 83 |  |  |  |  |

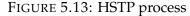

|   | 5.2                                                    | Novel Microwave Generator                             | 87 |  |  |  |  |

|   |                                                        | 5.2.1 Negative Pulse Generator                        | 87 |  |  |  |  |

|   |                                                        | Phase Control Circuit                                 | 88 |  |  |  |  |

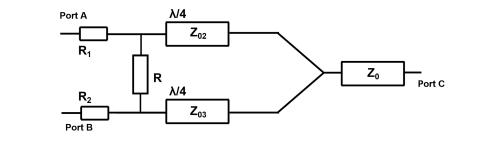

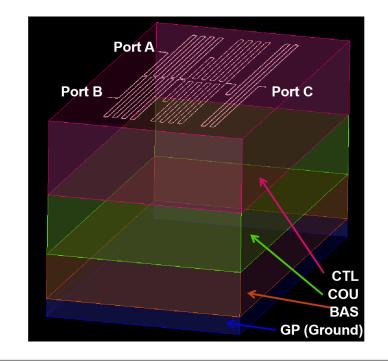

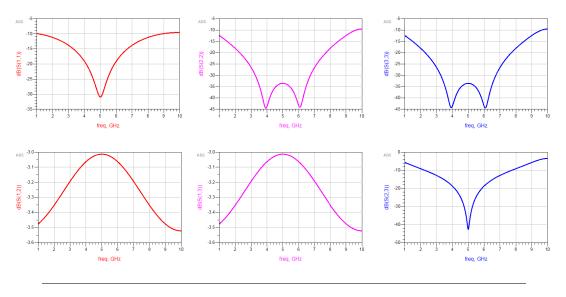

|   |                                                        | Wilkinson Power Divider                               | 90 |  |  |  |  |

|   | 5.3                                                    | Schematic and Simulation of Novel Microwave Generator | 93 |  |  |  |  |

|   | 5.4                                                    | Conclusion                                            | 94 |  |  |  |  |

| 6 | Con                                                    | clusion and Future Work                               | 95 |  |  |  |  |

## Chapter 1

## Background

## 1.1 Introduction

Quantum computer owns the advantage of parallel calculation so that the it can solve the development potential problem in the future[1]. It will play an ever more important part in the behaviour of many emerging forms of artificial nano-technology, and in our understanding of the nano-machinery of biological molecules [2]. The engineering of the ultra small will continue to advance and change our world in coming decades, and as this happens we might use quantum computers to understand and engineer such technology at the atomic level[3]. The context for the development of quantum computers may be explained by a more familiar quantum technology: the laser[4]. Laser' advent reveals a phenomenon: light was always 'incoherent',which means that the many electro-magentic waves generated by source was emitted at completely random times with respect to each other. Quantum mechanical effects allow these waves to be generated in phase, and the light source engineered to exploit this concept was the laser [2]. Based on that, quantum computer,which is engineered to control coherent quantum mechanical waves for different applications, will be quite different with ordinary computer.

The example task for quantum computers which has provided the foremost motivation for their development is Shor's quantum algorithm for factoring large numbers[5]. For example, Shor's algorithm addresses the computational challenge of factoring by exploiting quantum interference to measure the periodicity of arithmetic objects[5][6]. This is one among several quantum algorithms that would allow modestly sized quantum computers to outperform the largest classical supercomputers in solving some specific problems important for data encryption[2]. On the other hand, another application should be paid attention which brings a high impact: Feynman's 1980s proposal of using quantum computers for the efficient simulation of quantum systems[7].

Such as quantum computing 'software' is under research nowadays. Quantum computing 'hardware' is worth to be discussed as well. There are many possible materials for lasers — crystals, organic dye molecules, semiconductors, free electrons — and likewise there are many materials under consideration for quantum computers[2]. Quantum bit is usually recognized to be constructed from the smallest form of matter and an isolated system or unit, such as in ion traps and optical lattices[8].. Besides,they may likewise be made far larger than routine electronic components, as in some super-conducting systems[9]. Based on the study of superconductors, we will mainly discuss the control of superconducting qubit in this thesis.

### **1.2 Requirements For Quantum Computing**

To quantum computing, the most strict requirement is the 'closed box'. That means a quantum computer's internal operation, while under the programmer's control, must otherwise be isolated from the environment<sup>[10]</sup>. There is a phenomenon called decoherence excited in quantum computer. It is caused by small amounts of information leakage form the 'closed box'. Then it can disturb the fragile quantum mechanical waves where the quantum computer depends on. Decoherence comes in several forms. At first state, the quantum mechanical waves, or the oscillations of the constituents in quantum computers will reveal the interference phenomena. Because the constituents process in experiments, the phase of the waves loss the 'cohere' after a certain time. Thus, in an ensemble experiment. trial-to-trial variations in oscillator frequency lead to an apparent damping of wave interference on a timescale called  $T_2$ [11]. Then people discover that once a signal trial of a single quantum oscillator will keep the phase coherence longer than  $T_1$ . Finally, random process change the energy from oscillator, bring the system to thermal equilibrium on a timescale called  $T_2$  [11]. Fundamentally  $T_2 \leq 2 \times T_1$  and for most system,  $T_1$  will be much larger than  $T_2$ . To prolong the  $T_2$  becomes a research subject nowadays.

Besides the coherence time, there are some features which is people nowadays care about. The first thing is scalability. People expect the quantum computer operate in a Hilbert space. One single qubit can be simulated by LC classic oscillator. Because the quantum mechanic allows the entanglement, the logic space can potentially be described by a very large group[12]. This entanglement state can not be described by many signal classical oscillators or qubits[13]. Finally it is the large Hilbert space of a quantum computer that allows it operations unavailable to classical computers. For qubits, the size and energy of a quantum computer generally grows linearly with N and the resources to define or control the qubit are diverse[13]. They may include space on a microchip, classical microwave electronics, dedicated lasers, cryogenic refrigerators, and so on. For a scalable system ,these resources must be made scalable as well, which invokes complex engineering issues and the infrastructure available for large-scale technologies. That leads it difficult to make quantum system scalable.

The second thing is Universal logic. This is particularly important in quantum computers. To standard quantum computing,, it is sufficient to have available nearly 'analogue' single-qubit gates. For example, arbitrary flux direction for one flux qubit. Almost any 'digital' entangling two-qubit can be described logically, such as controlled-NOT gate. People use the logic gate to structure the quantum algorithm such as Quantum Neural Network (QNN)[14]. On the other hand, not all quantum computer is need quantum getes [15]. In adiabatic quantum computation, one defines the answer to a computational problem as the ground state of a complex network of interactions between qubits, and then one adiabatically evolves those qubits into that ground state by slowly turning on the interactions. In this case, evaluation of system is different with first case. Whether the system is complex enough and how long it takes to keep the temperature or turn off the temperature to search the best value of problem become main object detected[16]. Adiabatic quantum computers is near to gate-based computer in power consumption, but it is simpler for technologies.

The most important requirement for quantum computer is correctability[17]. It means that quantum computer must be possible to extract the entropy of the computer

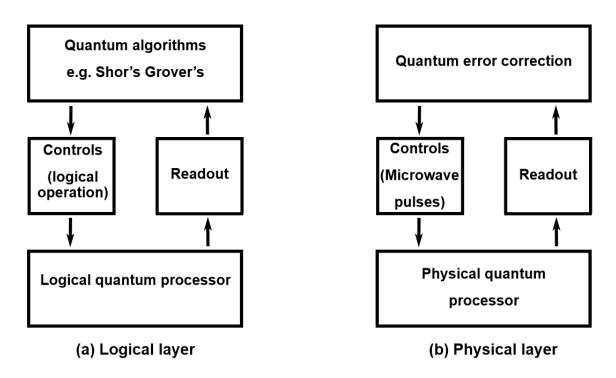

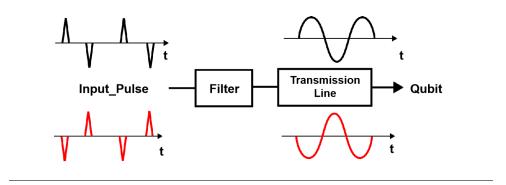

FIGURE 1.1: A systems view of a QEC processor

to maintain the computer's quantum state. Even if it is possible to achieve excellent isolation of quantum computer from environment, no one can execute quantum logic gates with perfect accuracy. Like an analog classical computer, the errors in the quantum gates form a continuum. Errors accumulate over the course of a computation in the gates and cause fault. A device that works effectively even when its elementary components are imperfect is said to be fault-tolerant[18]. Actually, similar problem arise in the theory of fault-tolerant classical computation. However, silicon-based circuitry is remarkably reliable, fault-tolerance is not essential to the operation of modern digital computers<sup>[19]</sup>. In 1952, Von Neumann suggested improving the reliability of a circuit with noisy gates by executing each gate many times, and using majority voting[20]. Although Von Neumann's theory has a shortcoming that he assumed perfect transmission of bits through the "wires" connecting the gates the assumption was proved by G'acs in 1983[21]. It gives us a enlightenment that fault-tolerant processing of quantum information may be achieved. The main challenge is to construct a universal set of quantum gates that can act on the encoded data blocks without introducing an excessive number of errors<sup>[18]</sup>. Some schemes for universal computation are outlined<sup>[22]</sup>.

### **1.3 QEC For Fault-Tolerant Computer**

As mentioned that the main challenge to achieve fault-tolerant process is to avoid large errors in basic quantum gates. Except the incomplete isolation environment, the increasing of qubit numbers will arise the noise. Some significant steps has been achieved such as Alexei Kitaev[23]. The reason is that the information is stored in the qubit as a quantum computer. Qubit is required to interact with each other strongly,

FIGURE 1.2: The physical qubit processor

external inputs for control, and outputs for detection. It is hard to balance the enough control and coupling because of preserving quantum coherence. This conflict represents a fundamental impediment to reducing the physical qubit error rate low enough to perform long/difficult/large-scale/practical quantum computations with them directly[24].

Fortunately, it has been shown that with quantum error correction (QEC) it is possible to perform fault-tolerant quantum computing[25]. The essential idea for QEC is to store information using a larger physical space that are isolation to noise. The particular architecture for implementing a fault-tolerant operating scheme has bearing on the requirements necessary for the underlying physical qubits<sup>[26]</sup>. A full fault-tolerant quantum computing system is presented within a layered structure as shown in Fig. 1.1. QEC can achieved by two primary layers, a physical qubit layer and a logical qubit layer[27]. Physical layer contains the qubit which constitute the physical quantum processor. The processor uses the measurement outcomes of the physical qubits to realize a QEC code. This classical processor keeps track of the physical errors, and implements the appropriate feedback on the controls of the physical qubits[27]. On the other hand, logical layer functions through control of the physical layer. Logical qubits are encoded within the physical qubits, and logical controls and readouts are governed through a processor that determines how to implement difficult quantum algorithms, e.g. Shor's, Grover's, and quantum simulation[28][29]. Many types of qubits has been explored applied in experimental systems, such as superconducting qubits, trappedion and so on. For purpose of quantum computing, it is important to normalize decoherence time to the quantum gate lengths. That means the longer decoherence time for qubit, the more operations can be finished. As now, the superconducting qubits holds the potential of hundreds  $\mu s$  decoherence time and each quantum gate takes several 10 ns, the number of operations per coherence time becomes a very promising number (almost 1000 operations).

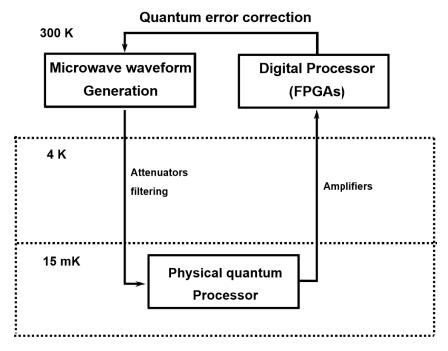

Fig. 1.2 presents the physical qubit schematic. Microwave pulses are generated

FIGURE 1.3: Approach to interfacing the quantum process and classical computer

at room temperature using synthesizers, arbitrary waveform generators, and mixers. These pulses are filtered and attenuated to input to the qubit. High-fidelity readout of the qubit state requires quantum-limited and other cryogenic amplification to overcome thermal noise for digitization and weighted measurement[30]. Physical control and readout function is orchestrated by digital process (FPGAs) to perform the error correction protocol.

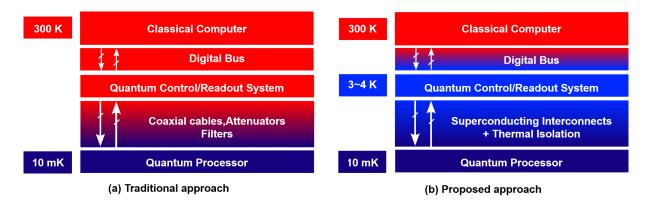

### **1.4 Researc Purpose**

As presented in Fig. 1.2, the microwave generator is placed at room temperature. However, it is possible that these feedback loop can be implemented within low temperature although it is start from Cryogenic-CMOS technology[31][32]. Fig. 1.3 presents the traditional and proposed approach to achieve the loop which connect the quantum process and classical computer. Currently,quantum process system can be realized by using signal from room-temperature. Here, quantum process is connected to classical computer using meters of lossy coaxial cables which is shown as (a). In the future,the quantum process will be scaled to million qubit level. The control and readout system must be integrated and implemented in "near" to quantum process to avoid too many cables. For this purpose, several research propose that to scale the quantum control and readout system within cryogenic temperature which is shown as (b). If the control and readout system is implemented within cryogenic temperature, the circuit based on Josephson Junction (JJ) becomes feasible.

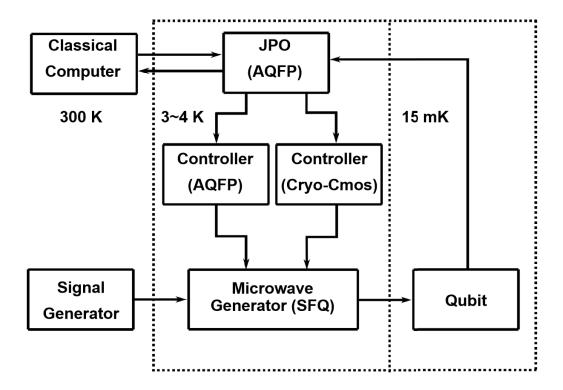

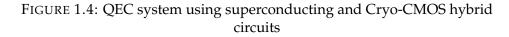

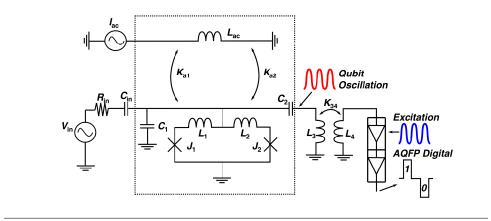

Our work seems to be significant which is currently underway toward implementation of the schematic presented in Fig. 1.4. The room-temperature continues signal is applied to cryogenic microwave generator which is designed by single flux quantum circuits (SFQ)[33]. And cryogenic microwave is generated and drive qubit which is under 15 mK. The driven qubit will cause the Ribi oscillation so that qubit state can be readout by Josephson parametric oscillator (JPO) by compare the phase shift[34]. AQFP cell can readout the oscillation phase and to improve the sensitivity, we design the integrator. On the other hand, the there are two sides to control the microwave generator. We design the microwave duration controller using AQFP circuits and microwave envelope controller using Cyro-CMOS technology. Thus, we can structure the

#### QEC system using superconducting and Cryo-CMOS hybrid circuits

simple feedback loop to achieve qubit controlling. Besides, we suggest some improvement to this system and fabricate the chip using HSTP process.

This thesis is divided into 5 parts and content of each chapter is list as follows:

The first chapter describes the background about the quantum process

The second chapter describes the microwave generator design within 4.2 K and measurement result.

The third chapter describes the microwave duration controller and integrator applied in JPO using AQFP including measurement result.

The forth chapter describes the microwave envelope controller using Cryo-CMOS technology including measurement result.

The fifth chapter describes the improvement of this system.

The sixth chapter describes summary of this thesis.

## **Chapter 2**

## **Microwave Generator Using SFQ**

In this chapter, we describe the microwave generator structure with fundamental elements. We will start from characteristics of superconducting circuits based cell which including JJ and SFQ family cell. Then we will introduce the operation principle of microwave generator. Finally we will state the measurement environment of microwave generator and show the measurement result

## 2.1 Josephson Junction

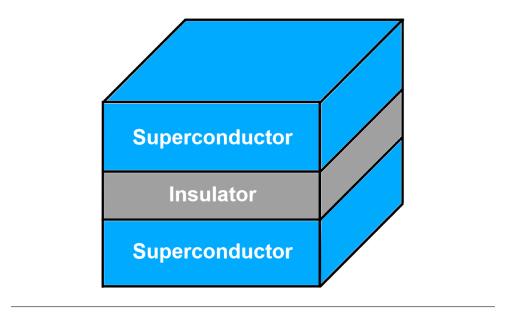

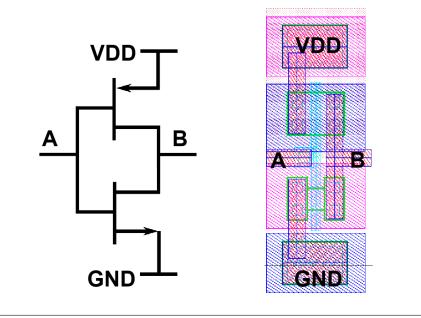

FIGURE 2.1: Model of Josephson junction

The most important cell of superconducting circuits is Josephson junction (JJ) and model is presented as Fig. 2.1. JJ consists of two superconductors where there is a insulator between them. This structure is know as SIS and if the insulator is thin enough, electrodes in superconductor can tunnel though the barrier. This phenomenon is called quantum tunneling effect and if allows current crossing the insulator barrier even if there is no external biased voltage. The crossed current of JJ is called Josephson current and the value can be given as follows:

$$I = I_c sin(\theta_1 - \theta_2) = I_c sin(\phi)$$

(2.1)

Here  $\theta_1$  and  $\theta_2$  is the phase factor of two superconductor,  $\phi$  is the phase difference between  $\theta_1$  and  $\theta_2$ .  $I_c$  is the critical current of JJ. Phase changes with time will arise the voltage linearly in superconductor with following formula:

(

$$\frac{\partial \Delta \phi}{\partial t} = \frac{2e}{\hbar} V \tag{2.2}$$

Here *V* is the voltage caused by switching JJ, *e* is elementary charge and  $\hbar$  is the reduced Planck constant. From the previous formula, one thing is revealed that alternative current cross though the junction, which is also called AC Josephson effect.

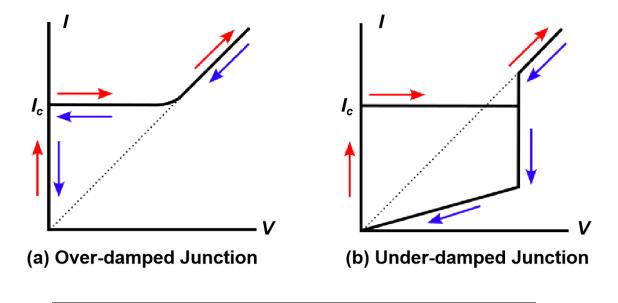

FIGURE 2.2: Equivalent circuit of a Josephson junction

To achieve the small-signal analysis of JJ, we present the equivalent circuit model of JJ which is shown as Fig. 2.2. Here the resistance *R* and capacitance *C* is shunted to JJ and  $\phi$  is phase difference of two ports of JJ. We analyze this model based on Thevenin's equivalent theorem and the formula can be presented as follows:

$$I = I_c sin\phi + \frac{V}{R} + C\frac{dV}{dt}$$

(2.3)

Then we can combine the two formula (2.4) and (2.5), the formula can be presented as follows:

$$I = \frac{\hbar C}{2e} \frac{d^2 \phi}{dt^2} + \frac{\hbar}{2eR} \frac{d\phi}{dt} + I_c sin\phi$$

(2.4)

The new time variable  $\tau$  is available as follows:

$$\tau = \omega_c = \frac{2eI_cR}{\hbar}t \tag{2.5}$$

In conclusion of these formula, we can get as follows:

$$\frac{I}{I_c} = \beta_c \frac{d^2 \phi}{d\tau^2} + \frac{d\phi}{d\tau} + \sin\phi$$

(2.6)

The parameter  $\beta_c$  is McCumber parameter defined as

$$\beta_c = \omega_c CR = \left(\frac{2e}{\hbar}\right) \cdot (I_c R) \cdot (CR) = \frac{2eI_c R^2 C}{\hbar}$$

(2.7)

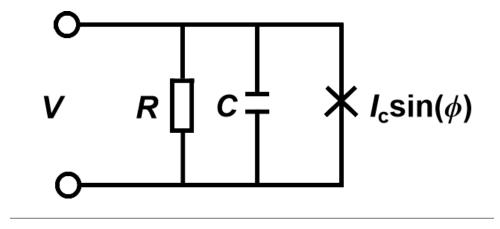

Besides the AC Josephson effect, there is also a DC Josephson effect. It is much easy to understand that if the current *I* cross though the junction is smaller than  $I_c$ , there will be no voltage because circuits is under superconducting state. On the other hand, if the current *I* is larger than  $I_c$ , the superconducting state will be destroyed and there is voltage arisen on JJ.

FIGURE 2.3: I - V characteristic of Josephson junction

$\beta_c$  is mainly decided by shunt resistor *R* because capacitance *C* is almost decided by process. According to formula (2.6), the *I* – *V* characteristic of JJ can be calculated if we set the  $\beta_c$  to a constant. However, the the *I* – *V* characteristic of JJ will be changed in different case of  $\beta_c$ . If  $\beta_c$  is about constant 1, the voltage of JJ will decay to 0 very fast once the large current *I* cross though junction. On the other hand, if  $\beta_c$  is about constant 0, the voltage of JJ will holds on a time until the current decay significantly. For these two different cases, we can present the figure which is shown in Fig. 2.3. Over-damped Junction is the situation that  $\beta_c$  is smaller than 1 and Under-damped Junction is the situation that  $\beta_c$  is bigger than 1.

### 2.2 Signle Flux Quantum Logic Circuits

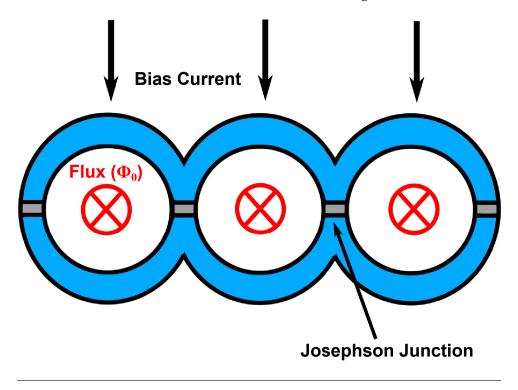

Based on magnetic flux quantization theory, magnetic flux exists in a superconducting contour loop can be quantized and the minimum magnetic flux unit is shown as  $\Phi_0$ . Based on this character, we can store information in the loop with form of magnetic flux. Once a magnetic flux escapee from the loop, there is a pulse signal generated by JJ because junction switches. So that we can transport the flux message by switching the JJ. The imagination photo of SFQ circuits is presented as Fig.2.4. The value of  $\Phi_0$  is presented by following formula:

$$\Phi_0 = \frac{h}{2e} = 2.07 \times 10^{-15} \text{Wb}$$

(2.8)

$$\Phi = \int V dt = \int \frac{\Phi_0}{2\pi} d\phi = \Phi_0$$

(2.9)

The escape flux value is  $Phi_0$  when JJ switches. Besides, we can get the flux on JJ according to the Faraday's laws which is presented in (2.9). The phase of JJ changes  $2\pi$  once the JJ switches. JJ phase changing cause the voltage of JJ changing, which means the pulse is generated on junction. Thus, we can set one  $\Phi_0$  as an information carrier to achieve the SQF logic, where the generated pulse signal represents the logic "1".

Fig.2.4 presents the physical layer of SFQ circuits and the superconducting circuits loop are connected serially. Adjoining loop use the same junction (grey) and junction connect to junction with inductance (blue). Extra bias current is required to each loop because it can provide an initial current to JJ so that it can switches more easily. When there is a flux (red) escape from the loop, the current in the loop rotate clockwise and the value can be calculated as follows:

$$I \cong \frac{\Phi_0}{L} \tag{2.10}$$

Here the *L* is the inductance of superconducting loop. If the  $I > I_c$ , JJ switches and delivers the quantum flux to the next loop. On the other hand, if the  $I < I_c$ , JJ will not switch and the flux will store in the loop. Generally, this case is caused because the inductance *L* of loop is very big so that the current changes very small according to (2.10). Both two situations can be used to design the SFQ circuits. The time of JJ switches is very fast, which is about several picoseconds. The amplitude of SFQ voltage can arrive about hundreds of microvolts according the formula (2.9).

FIGURE 2.4: Imagination of SFQ circuits operation

## 2.3 SFQ Logic Gate

As mentioned, we can use the characteristic of flux transmission in superconducting loop to achieve logic message. Nowadays we have build up the SFQ cell library based on the transmission and storage functions of SFQ circuits. The section we will introduce some basic SFQ logic cell which is the elements to form the digital applications.

#### 2.3.1 Josephson Transmission Line (JTL)

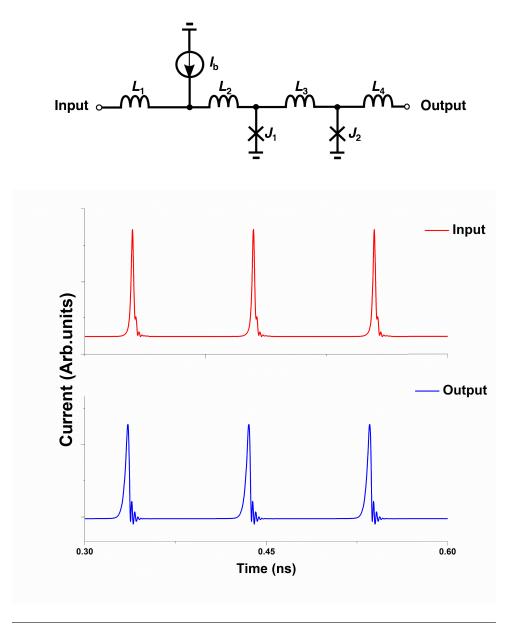

FIGURE 2.5: Josephson transmission line

The structure of Josephson Transmission Line (JTL) is presented as Fig.2.5. It contains just two JJs and several inductance. When there is one pulse input though the inductance  $L_1$ , the loop which contains the  $L_2$  and  $J_1$  will store this flux message and the current which across though the  $J_1$  becomes big. When current is beyond the critical current of  $J_1$ ,  $J_1$  switches and phase of  $J_1$  turns 2 $\Pi$ . Then there will be a flux store in loop which contains the  $J_1, L_3, J_2$  because of  $J_1$  switches. The changing phase of  $J_1$ also cause the changing phase of  $J_2$  if inductance  $L_3$  is not too big to store a flux. With this processing the JJ will switch one by one and propagate SFQ pulse. The simulation result is presented at bottom of Fig. 2.5. As the result, JTL can propagate an SFQ pulse from port "input" to "output".

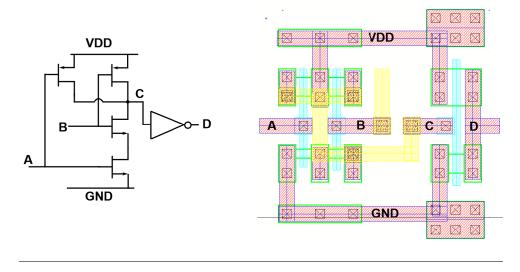

#### 2.3.2 Confluence Buffer (CB)

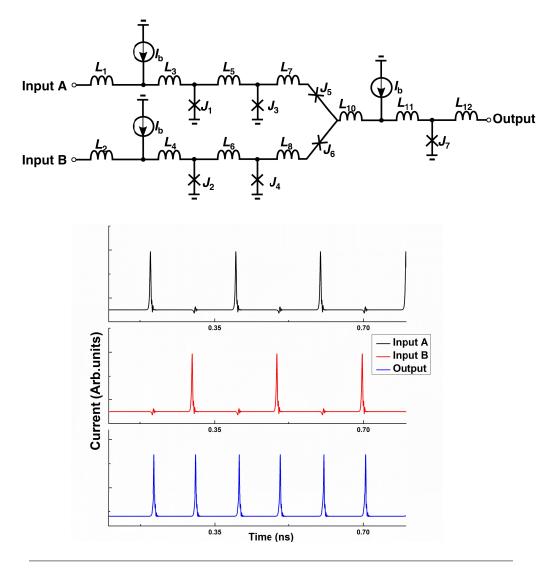

FIGURE 2.6: Confluence buffer

Here we present a structure of confluence buffer (CB) to discuss the situation that two pulses input to one superconducting loop. The structure is presented in top of Fig.2.6. The input A and input B propagate a pulse though inductance  $L_1$  and  $L_2$ . The loop which contains the  $J_1$ ,  $J_3$  and  $J_7$  propagates the pulse signal when there is a pulse exist at input A. With the same operation, the loop which contains the  $J_2$ ,  $J_4$  and  $J_7$ propagates the pulse signal when there is a pulse exist at input B. Thus, the SFQ CB cell can reproduce an SFQ pulse once there is an incoming SFQ pulse input from any input. To prevent the wrong direction of transmission such like pulse pass though the  $J_7$  and pass though the  $J_8$ , the  $J_5$  and  $J_6$  are inserted between the  $L_7$  and  $L_8$ . Because the  $J_6$  switches earlier than  $J_4$ , it disrupts the loop and prevents the SFQ pulse from propagating in the wrong direction. In addition,  $J_5$  perform the same function with  $J_6$  to when an pulse signal is propagated from input B. If the pulses are input at the same tame, the error will occurs because CB just can generate one pulse at one time. The simulation is presented at bottom of Fig.2.6. Output hold the almost same time interval between both sides of SFQ pulse input.

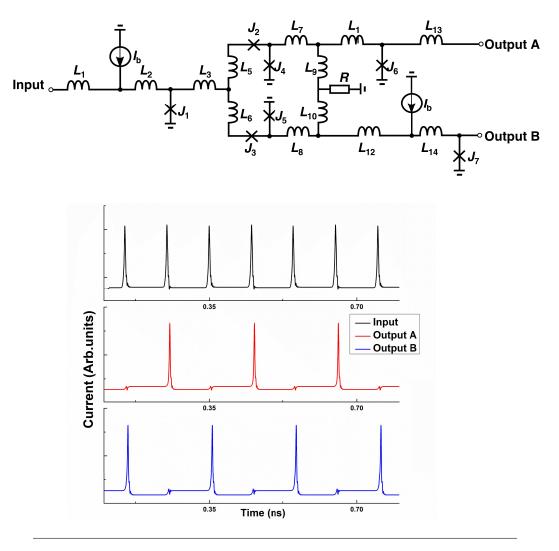

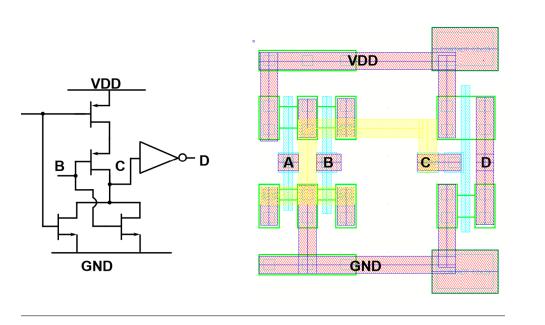

#### 2.3.3 T-Flip Flop (TFF)

FIGURE 2.7: T-flip flop

Here we introduce the T-flip flop (TFF) whose function is inverse with CB. The structure is presented at top of Fig.2.7. Pulse is propagated though inductance  $L_1$  from input port. There are two loops share one JJ ( $J_1$ ), which are  $J_1, J_2, J_4$  and  $J_1, J_3, J_5$ . When first pulse is propagated, the  $J_2$  will switch earlier than  $J_3$  because the critical current of  $J_2$  is smaller than  $J_3$ . So that the phase of  $J_2$  turns 2 $\Pi$ . Thus, the phase of JJ ( $J_5$ ) will

switch and propagate one pulse signal though the inductance  $L_14$  to output B. On the other hand, the loop which contains the  $J_5$ ,  $L_8$ ,  $L_10$ ,  $L_9$ ,  $L_7$ ,  $J_4$  store a flux because the phase of  $J_5$  turns 2II. This case the  $J_4$  does not switch so that there is a large current store in the inductance  $L_9$  and  $L_10$ . When second pulse is propagated though  $L_1$ , the  $J_4$  becomes much easier than  $J_5$ . Thus, the  $J_4$  switches and  $J_5$  keep the state in this case. The pulse signal generated by  $J_4$  is propagated though inductance  $L_13$  to output A. After that, the loop of  $J_5$ ,  $L_8$ ,  $L_10$ ,  $L_9$ ,  $L_7$ ,  $J_4$  recover initial state and current in  $L_9$  and  $L_10$  reduce. Therefore, the function of TFF can be realized that input pulse is divided in two parts in sequence. The simulation of TFF cell is presented at bottom of Fig.2.7. The function can be confirm according to the simulation result when the frequency of pulse signal arrives about 10GHz.

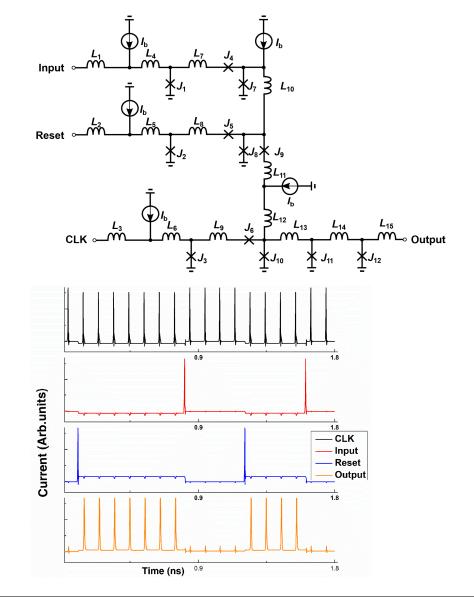

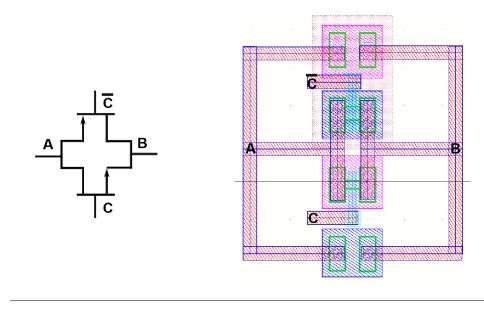

#### 2.3.4 Non Destructive Read Out (NDRO)

Here we preset the structure of Non Destructive Read Out (NDRO) at top of Fig.2.8. Generally, the continues pulses sequence is propagated though the inductance  $L_3$  from CLK port. Because the critical current of  $J_6$  is smaller than  $J_10$ ,  $J_6$  will switch earlier than  $J_10$  when  $J_3$  switches. Thus the flux in loop which contains the  $J_10, J_6, J_3$  will not be propagated into next loop. Oh the other hand, if there is a pulse which is propagated though the  $L_1$  from input port, junction  $J_7$  will switch. In this case the loop which contains  $J_3, J_6, L_4, L_9, J_5$  stores a flux. The current in inductance  $L_5$  will increase and current inductance  $L_4$  will decrease. That means the junction  $J_3$  become hard to switch than  $J_2$ . Thus, next pulse which is propagated from input again will not impact the state because  $J_4$  switches earlier than  $J_7$ . So the current in the inductance  $L_12$  will increase and junction  $J_10$  become easy to switch. So after that if pulse is propagated from CLK port, junction  $J_10$  switches earlier than  $J_6$  and pulse signal can be propagated to output port.

On the other hand, if there is a pulse which is propagated thought  $L_2$  from reset port. The junction  $J_8$  will switch and it leads to  $L_9$  switch. Then the stored flux escapes from loop which contains the  $L_10, J_7, J_8$ . The current in inductance  $L_10$  decreases and junction  $J_10$  becomes hard to switch. So after that if pulse is propagated from CLK port, junction  $J_6$  switches earlier than  $J_10$  and pulse signal can be prevented to propagate to output port.

The simulation result is presented at bottom of fig.2.8. According to result, we can get the pulse sequence (black) only can be propagated during the period between the input and output. NDRO can be used as a switch to control the pulse sequence or registration which can store the information.

FIGURE 2.8: Non Destructive Read Out

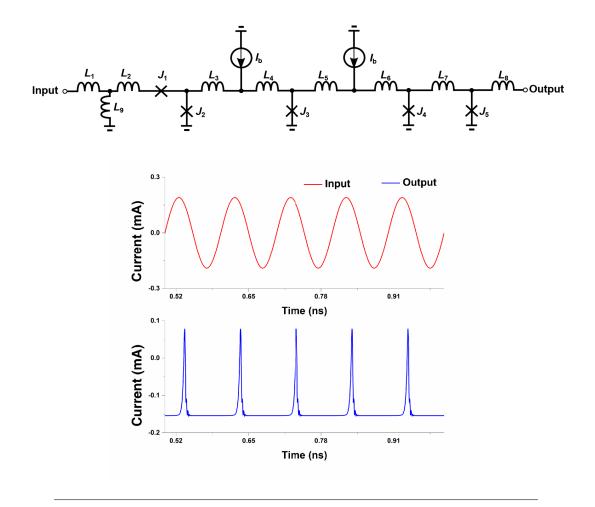

### 2.3.5 DC/SFQ Converter (DSC)

Here we present a SFQ cell which can convert the non-SFQ signal to SFQ pulse. The structure is presented as top of Fig.2.9. The signal come from input port, generally it is current signal. Once the current is big enough, the junction  $J_2$  will switch and generate a pulse signal to output prot. When the voltage drops, the current flows in the DC direction, so the SFQ is released by switching the escape junction J1 so that no output can be obtained. The simulation result is given at bottom of Fig.2.9. When input signal arrives at top, one pulse will be generated and propagated from output port. This cell realize the function that converter current signal to SFQ pulse signal.

FIGURE 2.9: DC/SFQ Converter

### 2.4 Qubit Control

In this section, we will mainly introduce the Microwave pulse generator. Firstly, we will discuss the generated microwave's to state of qubit. Thus, we will decide the parameter of microwave which we should pay attention. Then we will present the structure of microwave pulse generator and explain the operation function. Last we will present the measurement environment and result.

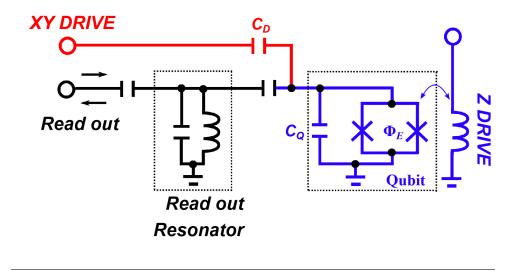

#### 2.4.1 Flux-Tunable Transmon Qubit

Here we present the schematic of a flux-tunable transmon qubit which contains the h XY-drive, Z-drive, and readout ports at Fig.2.11. The target qubit consists of capacitor  $L_Q$  in in parallel with a Josephson junction loop. The JJ can be thought of as a non-linear inductance which formulla is given as follows:

$$L_J = \frac{L_c}{\cos(2\pi\Phi_E/(\Phi_0))} \tag{2.11}$$

$$L_c = \frac{\Phi_0}{2\pi I_c} \tag{2.12}$$

FIGURE 2.10: Flux-Tunable Transmon Qubit

Here, the  $\Phi_E$  is the external flux across the loop,  $\Phi_0$  is the flux quanta.  $L_c$  is decided by critical current of JJ which is influenced by proportional junction area. Based on that, the flux-tunable transmon qubit can be thought of as a frequency-tunable nonlinear LC resonator. The transom qubit will behave quantum mechanically when the temperature is cooled to suppres the thermal population of the non-linear resonator. Generally, the effective photon temperature is approximately 250 mK for the typical qubit frequency of 5GHz. Thus, if the devices are close to several mK, the thermal excitations are sufficiently suppressed.

To control the qubit state, the XY-drive (red) should be used which is presented in Fig.2.11. The excitation frequencies of XY influence the spectral width of microwave excitation pulses. Generally, the the anharmonicity of qubit should be as large as possible in order to achieve more operations before the decoherence time.

The Z-drive (blue) port provides control of the qubit frequency by using an external current. This play an important role in system which can realize several operations: control of the qubit frequency, multi-qubit connection and qubit initialization. In this research we assume that the Z-plane can set the qubit frequency of 5Ghz and do the initialization.

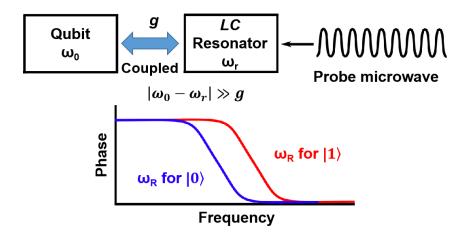

Actually, the qubit state can be readout by capacitively coupling an ancillary linear resonator (black). The coupling between the readout resonator and the qubit will cause a dispersive frequency shift of the readout resonator up or down in frequency. The readout resonator will interrogate at the average of two frequencies which behave the qubit state  $|0\rangle$  and  $|1\rangle$ . Then dispersive frequency shift will produce a state-dependent phase shift on the interrogation signal, which can be detected and used to determine the state of the qubit.

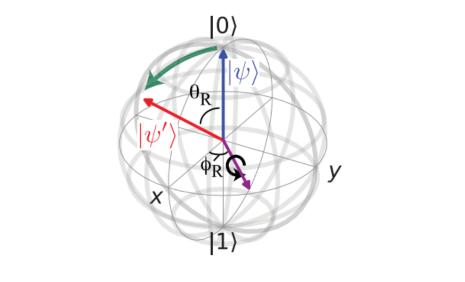

#### 2.4.2 Control of Transmon Qubit

Here we will discuss quantitatively about the control effect by XY-plane microwave signal. Assuming that voltage driven signal can be given as follows:

$$V_D(t) = a(t)\sin(\omega_D t) + (\pi - \phi_D)$$

(2.13)

Then the Hamiltonian of the driven circuit in the rotating qubit by the drive signal can be written as follows:

$$H_D \approx g \frac{a(t)}{2} (\cos(\phi_D \sigma_X) + \sin(\phi_D \sigma_Y) - \frac{h \pi \Delta_\omega}{4} \sigma_Z$$

(2.14)

Here the *g* shows the drive coupling strength which is decided mainly by capacitance  $C_D$  and  $C_Q$ .  $\Delta_\omega$  is the offset frequency which is the difference of driven frequency and qubit resonant frequency.  $\sigma_X, \sigma_Y, \sigma_Z$  is the Pauli spin matrices and formula is given as follows:

$$\sigma_{\mathbf{X}} = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}, \sigma_{\mathbf{Y}} = \begin{bmatrix} 0 & -i \\ i & 0 \end{bmatrix}, \sigma_{\mathbf{Z}} = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$$

(2.15)

FIGURE 2.11: Rotation of Qubit

Pauli spin matrices are always used in QEC system to perform the quantum error and quantum correction. It is also the basic quantum gate to achieve the quantum algorithm. Here we give the qubit rotation Imagine figure which refers to the thesis[9]. Once the microwave drive the qubit, the qubit which is shown at Bloch space will start to rotate. The Hamiltonian inflect the rotation and the formula is consisted by Pauli spin matrices. Here, Pauli-X gate perform the state reversal according to the formula (2.15). So turn back to the formula (2.14) we can get that the initial phase of microwave decides the qubit rotation direction. For example, if the initial phase is 0, the  $H_D$  is almost decided by  $\sigma_X$ . On the other hand, if the initial phase is  $\pi$ , the  $H_D$  is decided by  $-\sigma_X$ . It is desirable to only discuss rotations about the XY plane of the Bloch sphere. In Fig.2.11 ,/*theta*<sub>R</sub> reveals the rotation angle. According to the thesis[9], /*theta*<sub>R</sub> can be presented as follows:

$$\theta_R = 2\pi \frac{g}{h} \int_{t_0}^t a(t') \, dt'$$

(2.16)

The formula shows that the amplitude of microwave and the time which microwave keeps deciedes the state of qubit. The qubit is almost driven by XY-plane. On the other hand, the Z-plane can be calibrated by software[9] so that the qubit should nominally

be driven on resonance ( $\Delta_{\omega} = 0$ ). Although the amplitude of microwave and time duration do the combined action on qubit, the decoherence time of qubit limits the time duration. So the shorter time duration, the more power of microwave is required. Besides, during the time of microwave duration, the amplitude of microwave will influence the quantum fidelity[35]. Gate fidelity is a measure of how close the effect of an applied gate is to that of the desired unitary and can be limited by a number of factors, including control errors, noise, and decoherence[36]. Generally, the envelop of microwave, which behave the amplitude changes via time, is set to Gaussian function because it can arrive high fidelity though experiment[37]. In conclusion, we need the microwave signal which the duration and envelope can be controlled within cryogenic temperature.

#### 2.4.3 Filter Response of Pulse Signal

There is only pulse signal exist in SFQ circuits. To generate the microwave signal, we suggest a method that using pulse signal though the filter and we can get the microwave response. Here we analyze the different types of filter's impact on generated microwave. Here, we assume the the SFQ Pulse is ideal and response function of each types of filter can be given as follows:

$$F(\omega) = \begin{cases} K & -\omega_0 < \omega < \omega_0 \\ 0, & others \end{cases}$$

(2.17)

$$F(\omega) = \begin{cases} K & others \\ 0, & -\omega_0 < \omega < \omega_0 \end{cases}$$

(2.18)

$$F(\omega) = \begin{cases} K & -\omega_1 < \omega < \omega_2 \\ 0, & others \end{cases}$$

(2.19)

$$F(\omega) = \begin{cases} K & others \\ 0, & -\omega_1 < \omega < \omega_2 \end{cases}$$

(2.20)

Here, the *K* behaves the loss constant. Function (2.17) perform the frequency response of Low-pass filter. Function (2.18) perform the frequency response of Highpass filter. The  $\omega_0$  is the cut frequency of filter. Function (2.19) perform the frequency response of band-pass filter. Function (2.20) perform the frequency response of Band-stop filter. The  $\omega_1$  and  $\omega_2$  is the bandwidth of filter. SFQ pulse can be thought as an ideal impulse impact function ( $\delta(t)$ ). Thus one pulse input to filter, the response function can be presented on frequency domain as follows:

$$H(\omega) = 1 \times F(\omega) \tag{2.21}$$

Then we do the Fourier transform to the (2.21), the function on time domain can be given as follows:

$$h(t) = \frac{1}{2\pi} \int_{-\infty}^{\infty} H(\omega) \times e^{-j\omega t} d\omega$$

(2.22)

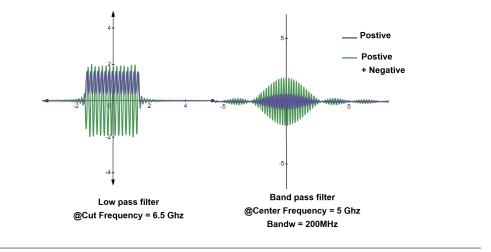

High-pass filter and Band-pass filter is not to be applied because the  $\delta(t)$  is high frequency signal. We can not obtain the microwave signal With the high frequency

component. Thus, we just discuss the Low-pass filter and Band-pass filter's impact on generated microwave.

To the low-pass filter, the function (2.22) can be presented as follows:

$$h(t) = \frac{K \times \omega_0}{\pi} sa(\omega_0 \times (t - t_0))$$

(2.23)

Here  $sa(x) = \sin(x)/x$ .

The cut frequency influence the output amplitude. However, the larger cut-frequency will arise external frequency component. Generally, we set it to from 5.5 to 7.5 GHz because of 5GHz qubit oscillation frequency. We can plot the function (2.23) and compare it to simulation result as Fig.2.12.

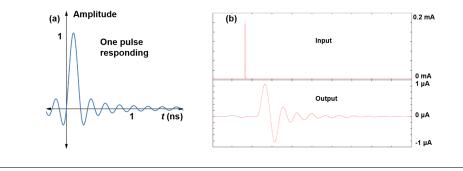

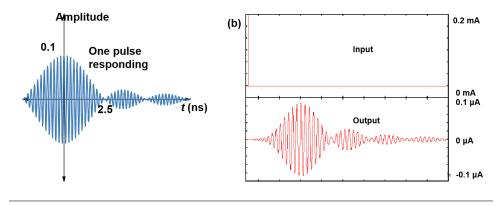

FIGURE 2.12: Mathematical model and simulation of One pulse response

In this case, the cut frequency of filter is 6.5 GHz and the loss constant is Independence with frequency. We use the JTL cell to generate a standard pulse and input to filter. The waveform of (a) and (b) is similar. According to the mathematical model, the approximate microwave can be generated and simulation result can be used to confirm. However, it is hard to control the amplitude of microwave only by one pulse. Lots of pulses are required to input to filter. We present the schematic as Fig.2.13.

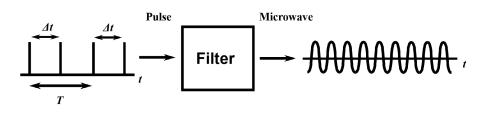

FIGURE 2.13: Mathematical model and simulation of one pulse response for low-pass filter

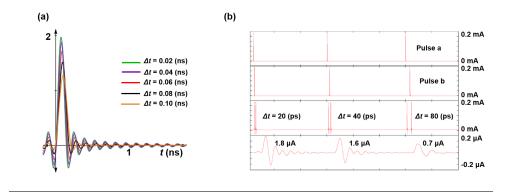

To control the amplitude of microwave, we suggest the schematic that pulse-pair to input to filter. The duration between each pulse-pair is main frequency component. It is obvious that time  $\delta(t)$  is smaller than *T*. Thus, the frequency component of  $\delta t$  will be removed by filter at output and keep the main frequency component of *T*. What's more, if we can control the interval of pulse-pair, the amplitude of microwave can be changed because pulse density changes. To confirm this theory, we present the Fig.2.14

In this case, we set the same filter to calculate the mathematical model and we input one pulse-pair. The interval of pulse-pair ( $\delta t$ ) decreases from the 0.1 nanosecond which

FIGURE 2.14: Mathematical model and simulation of pulse-pair response

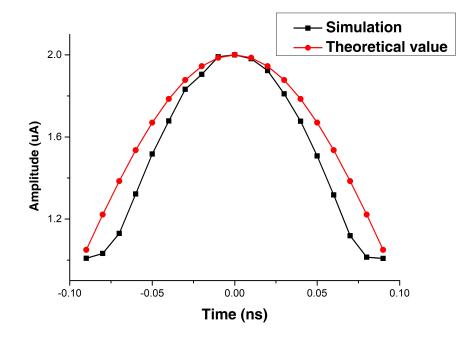

is the maximum value because we assume (*T*) as 0.2 nanosecond. Confluence pulse will increase the pulse density near-double so that the amplitude of microwave becomes double than before. Than interval of pulse-pair become longer which leads the pulse density smaller so that the amplitude of microwave also decreases like Fig.2.14 (a) shows. We also do the simulation to compare the waveform which is presented in Fig.2.14 (b). In this simulation we input two pulse (A and B) and use the Confluence Buffer to combine them. We have three examples to show the larger interval of pair-pulse, the smaller amplitude of microwave. Fig.2.15 present the relationship of amplitude of microwave and interval of pair-pulse in normalization. As the Fig.2.15 shows, the simulation variation trend is almost the same with theoretical value. The simulation value is smaller than theoretical value because the SFQ pulse is not ideal pulse signal. The circuits reflection is bigger than ideal model.

FIGURE 2.15: Mathematical model and simulation of pulse-pair response

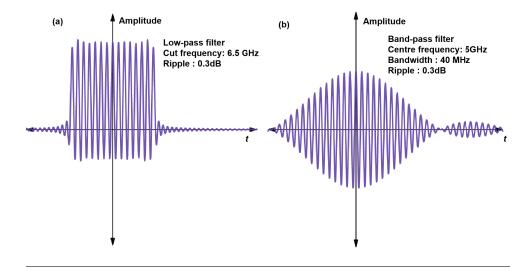

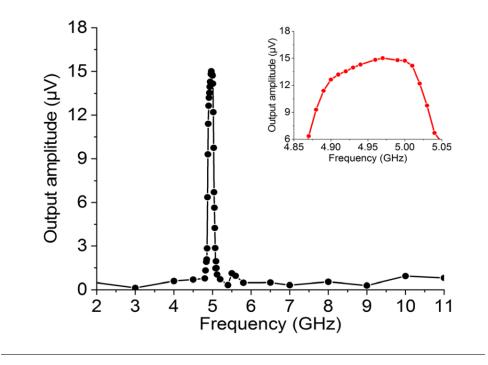

On the other hand, if we change the low-pass filter to band-pass filter, the microwave will be generated by applying the pair-pulse. The formula is given as follows:

$$h(t) = \frac{K \times \omega_0}{\pi} (sa(\omega_2 \times (t - t_0)) - sa(\omega_1 \times (t - t_0)))$$

(2.24)

Here, we assume  $\omega_2$  is bigger than  $\omega_1$ . The waveform is present in Fig.2.16. It is different with low-pass filter response as there is minus component in the function (2.20). Using one pulse into filter, the near-microwave signal can be generated directly. However, the amplitude will decrease largely using one pulse response. Besides, the tail can be found behind the main microwave. The tail lead to the transmission latency. We do the same simulation of band-pass filter response using one pulse. The result is similar with mathematical model. The reason why simulation microwave is asymmetric is that the initial state of circuits is start from 0. Also the circuits component such as impedance mismatch will arouse the asymmetric microwave. The amplitude is decrease to about 0.1  $\mu$  A which is match to calculated results.

FIGURE 2.16: Mathematical model and simulation of one pulse response for band-pass filter

So if we input the several pair-pulses into filter, the pair-pulses will be superposed and form the microwave signal both of low-pass filter and band-pass filter. The mathematical model is presented in Fig.2.17. The response of low-pass filter (a) has less latency because single pulse owns less ripple which can be found in Fig.2.12. However, the microwave generated by low-pass filter owns the DC component because the main value of pair-pulse is positive. Lots of pair-pulse sequence will lead the average value of microwave to positive which can be though the DC component. On the other hand, band-pass filter will avoid this phenomenon because single pulse response is longitudinal symmetry. However, the latency exist obviously which can be explained using formula (2.24). And the tail can be found which may influence the subsequent microwave form if the sequence is close to each other.

Both filter can generate the microwave to drive qubit by input the pair pulse. However, there is no consensus that which filter is better to generate microwave. Generally, People using the filter to decrease the thermal impact of quantum process. Most people use driven microwave generated by signal generator which is under roomtemperature. Thus, it is meaningful that apply two types of filter driven and compare effect in measurement. The amplitude of microwave can be controlled by changing the interval of pair pulse. Thus, the superconducting circuits to control the interval becomes very important.

FIGURE 2.17: Mathematical model and simulation of one pulse response for band-pass filter

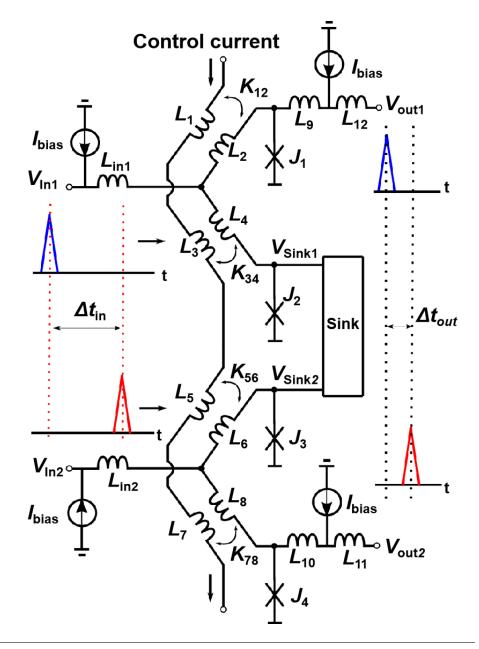

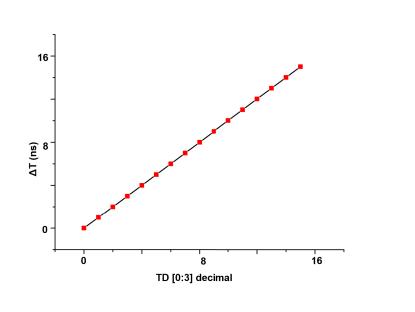

#### 2.4.4 Delay Generator (DG)

Here, we will introduce the designed delay generator using SFQ circuits. As mentioned, the amplitude of microwave can be controlled by changing the interval of pair pulse. So if there are two same pulses sequences, and we just make some controllable delay between these two pulses sequences and combine them using confluence buffer. The two pulse can be seen as a pair pulse and the delay is  $\Delta t$  which is the same with Fig.2.13. Original interval of pulse sequence can be seen as *T* which is the same with Fig.2.13. In our design, the time *T* is 0.2 nanosecond and  $\Delta t$  is less than 0.1 nanosecond. The large range of  $\Delta t$  is required.

The Structure is presented in Fig.2.18. Here, we input two sequences pulse sequences from inductance  $L_{in1}$  and  $L_{in2}$ . The initial interval of pulses of  $In_1$  and  $In_2$  is set to  $\delta t_0$  which is equals 0.1 nanosecond. The first pulses (blue) is propagated though inductance into loop which contains  $J_1, J_2, L_2, L_4$ . The  $J_1$  and  $J_2$  switches will switches at same time because the current cross the  $L_2$  and  $L_4$  is the same. It is the same situation of  $J_3$  and  $J_4$ . However, once there is control current input as Fig.2.18 shows, the initial state of JJs will change. With the current input, there is external flux input to the loops so that the current in the inductance  $L_2$  decrease because the opposite coupling between the  $L_2$  and  $L_1$ . On the other hand, the current in the inductance  $L_4$  increase. Thus,  $J_1$  will become switch harder than before. According to that the, the pulse which is generated by  $J_1$  will propagate slower than before and the pulse which is generated by  $J_2$  will propagate faster than before. Here, we choose the slower pulse to output and sink the faster pulse. The next pulse (red) input to the loop which does the same effect. The different thing is that we choose the faster pulse to output and sink the faster pulse. Thus, the original pulse interval ( $\Delta t_0$ ) becomes  $\Delta t$  by reconstruction of pulse sequences.

We need two loops to construct the DG. Although one loop can realize the pulse delay function, the latency is very small so that we have to connect several DGs to achieve enough range latency of pair-pulses. Small latency will also cause the error of confluence buffer which will be connect to DG easily. Therefore, that means the number of input ports and output ports should be same. Thus, we need two loop which own one input pulse and two output pulses. So that there will be two external outputs which should be sink.

FIGURE 2.18: Delay Generator (DG)

### 2.5 Microwave Generator With Pair Pulses

In this section will introduce the microwave generator structure and operation principle. Besides we will give the photo of fabricated chip and measurement result.

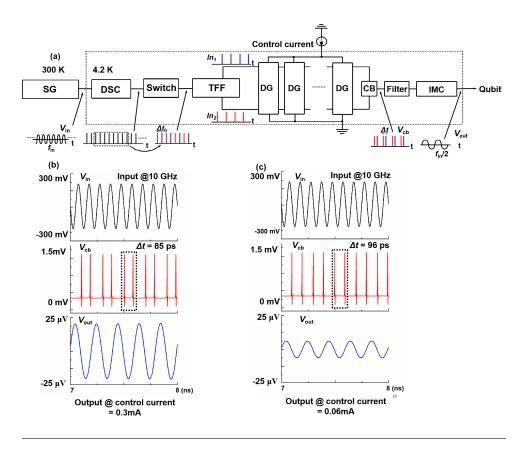

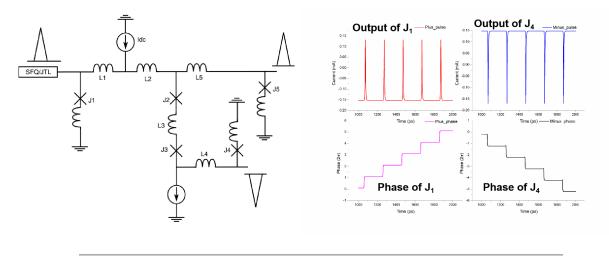

### 2.5.1 Microwave Generator

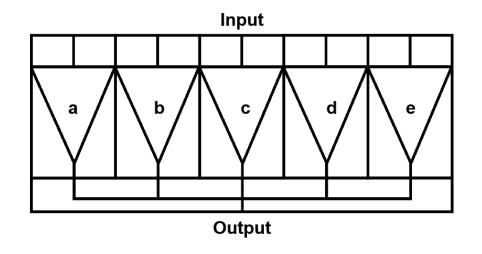

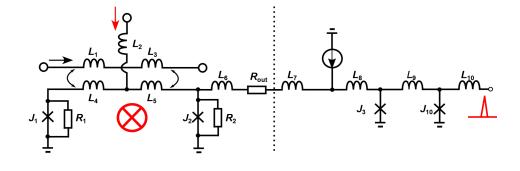

FIGURE 2.19: Microwave generator and operation principle

Here, we present the structure of microwave generator designed by SFQ cell in Fig.2.19. Here the SG is the signal generator, IMC is the impedance matching circuits. The structure is presented in Fig.2.19 (a).

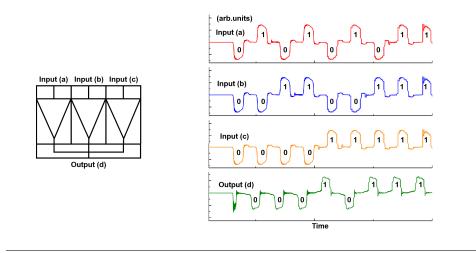

The point of the PP-MPG is that (i) the output microwave amplitude can be controlled by the time difference  $\Delta t$  between paired SFQ pulses, and that (ii) the output microwave frequency  $f_{out}$  is separated from the input microwave frequency fin as  $f_{out} = f_{in}/2$  to prevent the crosstalk between the input and output microwaves. The operation of the PP-MPG is as follows: A continuous microwave with a frequency of fin from a signal generator (SG) is applied to the DC/SFQ converter (DSC). Then, the DSC produces a continuous SFQ pulse train with an iteration frequency of  $f_{in}$ , and the following SFQ switch chops the continuous pulse train into a pulse train with an appropriate length. Furthermore, the two-output T flip-flop (TFF) lets the pulses from the SFQ switch travel to the two output ports alternatively, thus making two output pulse trains. Each pulse train includes half the number of the input pulses and thus has an iteration frequency of  $f_{in}/2$ . Moreover, the two pulse trains have a phase difference of  $\pi$ , i.e., a time difference of  $\Delta t_0$ .  $\Delta t_0$  is then changed to  $\Delta t$  by letting the two pulse trains travel through cascaded delay generators (DGs), the details of which will be explained later. Moreover, the confluence buffer (CB) merges the two pulse trains from the DGs and thereby produces a train of paired pulses, each with a time difference of  $\Delta t$ . Finally, a microwave pulse with a frequency of  $f_{out} = f_{in}/2$  and an amplitude determined by  $\Delta t$  is generated from the pulse-pair train by the filter and impedance matching circuit (IMC).

Figure.2.19 (b) and (c) show simulation waveforms of the PPG by a Josephson circuit simulator, JSIM, for  $f_{in} = 10 GHz$  and  $f_{out} = f_{in}/2 = 5 GHz$ , where  $V_{in}$ ,  $V_{cb}$ , and  $V_{out}$  denote the input microwave, the SFQ pulses from the CB, and the output microwave, respectively. The left-hand waveform are for  $\Delta t = 85 ps$ , and the right-hand ones are for  $\Delta t = 96 ps$ . The comparison between the left-hand and right-hand waveform clearly indicates that  $V_out$  changes with  $\Delta t$ . This is because as  $\Delta t$  decreases, the  $f_{in}$  component in  $V_{cb}$  decreases whereas the  $f_{out}$  component in  $V_{cb}$  increases.

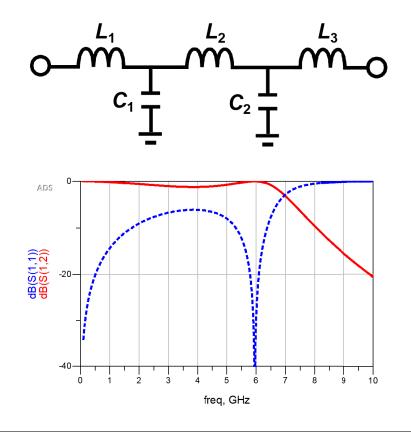

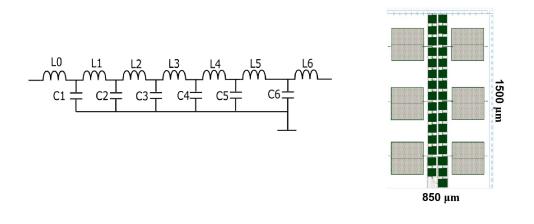

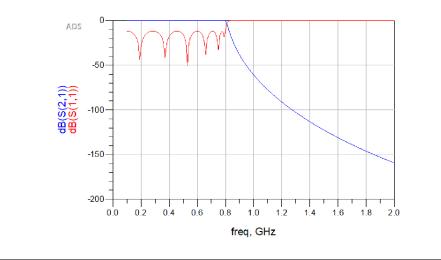

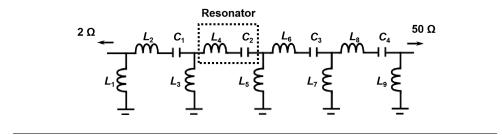

Low pass filter is presented at Fig.2.20. The typical T Type low-pass filter is applied with 2 stages. The simulation of S-parameter result is given at bottom. Simulator is Advanced Design system (ADS). Cut frequency of filter is about 6.5 GHz. Attenuation gradient is about 40dB/dec with 2 stages of filter for saving chip area. Here we use the low-pass filter to generate microwave. This part can be exchanged to band-pass filter and there is an improvement about removing the IMC which is applied in band-pass filter. This method will be introduced in the later chapters.

FIGURE 2.20: Low-pass filter

| No. | Parameter name          | Value                              |

|-----|-------------------------|------------------------------------|

| 1   | Chip Area               | $3000 \ \mu m \times 1000 \ \mu m$ |

| 2   | Input Signal Frequency  | 10 GHz                             |

| 3   | Output Signal Frequency | 5 GHz                              |

| 4   | Cut frequency of Filter | 6.5 GHz                            |

| 5   | Numbers of JJ           | 170                                |

| 6   | Bias Current (total)    | 20 mA                              |

TABLE 2.1: Chip parameter.

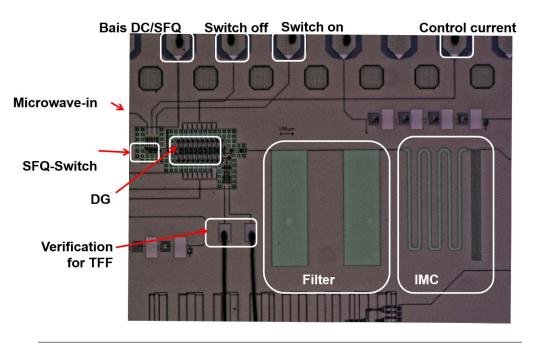

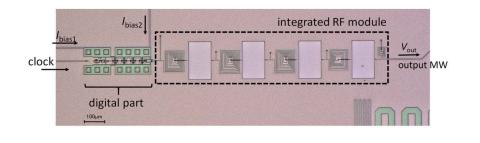

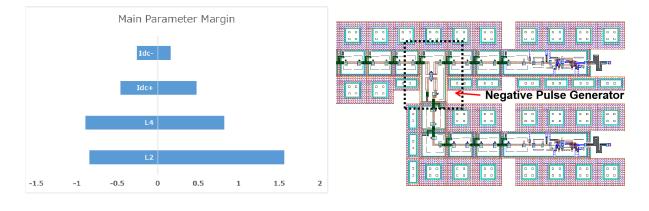

### 2.5.2 Photo and Parameter of Fabricated Circuits

Here, we present the photograph of microwave generator chip. The chip is fabricated by AIST  $10kA/cm^2$  Nb high-speed standard process (HSTP)[38]. The chip contains the verification function for TFF at low speed. Besides We set 8 DGs to expand the interval of pair pulse and all DGs apply the independent control current. The margin will be wide and system become controllable easily but it sacrifices the power consumption. It can be improvement in the future. The parameter is given as at Tab.2.1. Although the area arrives about 3000  $\mu$ m × 1000  $\mu$ m, the most area is the parts of low pass filter and IMC. As mentioned, the output frequency is close to qubit oscillation frequency which is 5 GHz. Therefore, the input frequency is set to 10 GHz according to the operation principle. Total bias current arrives about 20 mA because DGs arrays occupy lots of cells.

FIGURE 2.21: Photograph of chip

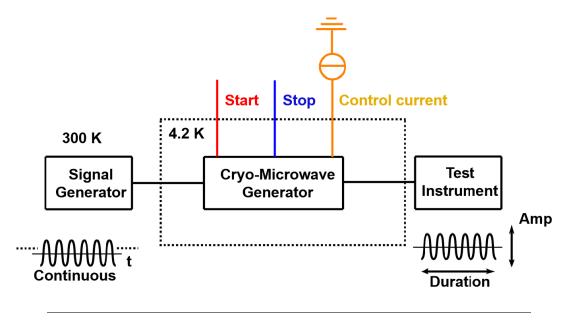

FIGURE 2.22: Measurement process

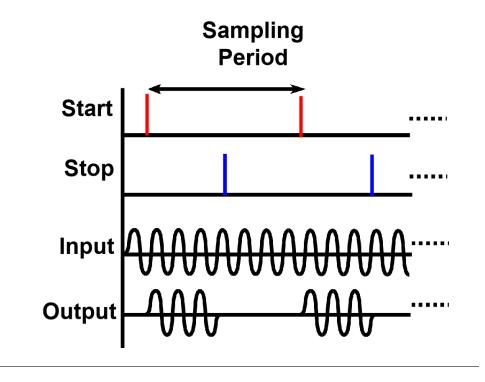

Then, we will introduce the environment of measurement. The most objects of investigation are duration time and amplitude of microwave as Fig.2.22. The continuous signal is input from room temperature, here, we set it to 10 GHz sine signal. The start (red) and stop (blue) SFQ pulse signal will control the duration of microwave. The control current (yellow) have impact on the amplitude of microwave. We put the circuits into liquid helium so that the environment temperature can be cooled down to 4.2 K. The test instrument can be chosen and it is spectrum analyzer generally.

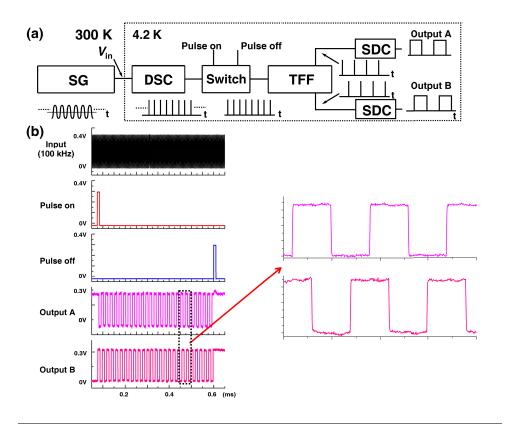

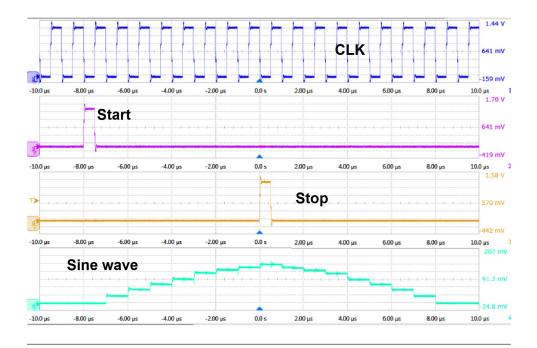

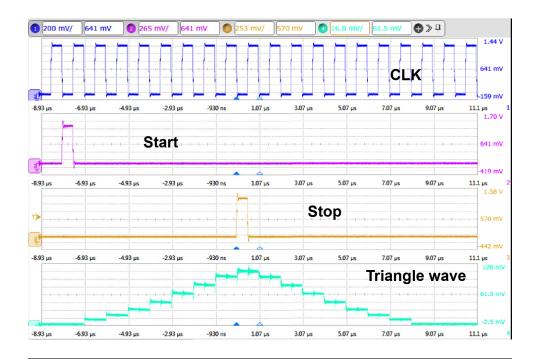

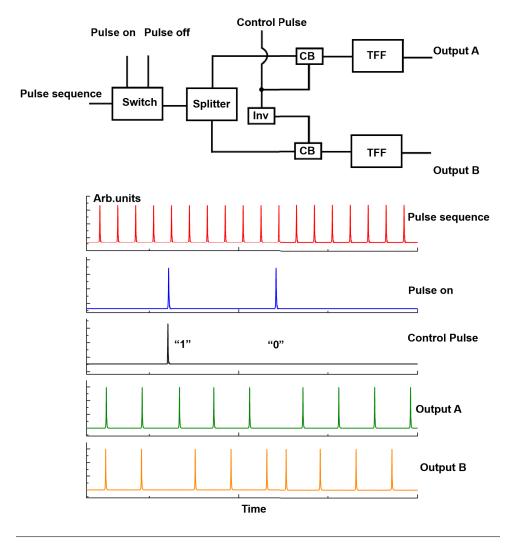

#### 2.5.3 Function Verification Under Low Speed

Here, we present the function verification process and result in Fig.2.23. In the function verification, we mainly pay attention on the TFF cells within low speed. Because the latency caused by DGs is very small, about several picosecond, it is very hard to be detected under low speed. Fig. 2.23 (a) illustrates the measurement method. We input a series of square wave within room-temperature. One square is transformed to one pulse on the chip. The pulse on and pulse off control the interval of the pulse sequence. Output of TFF is separated and detected by SFQ to DC converter (SDC). Fig. 2.23 (b) exhibits the experiment result. Here, the frequency of input pulse sequence is 100 kHz. The output of the TFF can be available only between the pulse on and pulse off. One rising or falling edge of output wave means one pulse generated. The result shows the TFF circuits divide the pulses well.

The function verification is required is that we can observe directly the SFQ pulse can be chosen by switch under low speed. It is hard to observe the generated microwave whether the duration has been chosen because crosstalk is very strong under high speed frequency. What's more, the generated microwave is small and it is mixed with noise. The function verification can help us to confirm the margin of DC bias current. Especially, the TFF cell is important for generating microwave. It is better to get the margin under low speed in advance of high speed measurement.

FIGURE 2.23: Operation function of verification under low speed

#### 2.5.4 Measurement Under High Speed

#### **Duration Measurement Under High Speed**

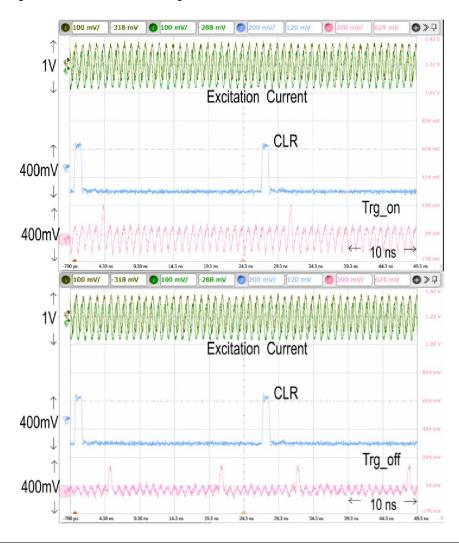

on Fig.2.24, we can adjust the duration of start (red) and stop (blue) signal to control the duration of microwave and the phenomena has been observed directly under low speed. The sampling period is decided as fig .2.24 shows. The interval between start and stop will change the duty ratio of microwave which will reflect on the measurement result obtained by spectrum analyzer. Under duration measurement, we set the control current to a constant.

FIGURE 2.24: Duration measurement process

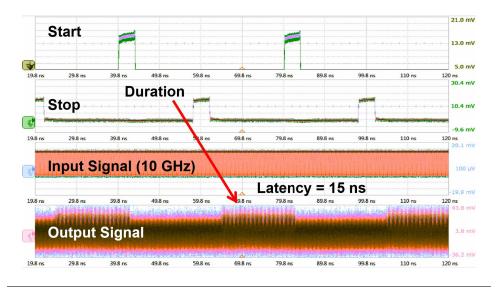

In this case we use oscilloscope to observe the waveform firstly. The signal should be amplified by 36 dB so that can be observed theoretically. The result is presented on Fig.2.25. Here, we apply the input output signal continuously to observe the waveform. The color grid method should be used to do the statistics on probability of microwave. According to the measurement, there was a small increase in the output signal at period of start and stop. The transmission latency is about 15 ns mainly caused by prob and test instrument.

FIGURE 2.25: Microwave detection on oscilloscope

Then, we will use the spectrum analyzer to detect the sampling frequency whether

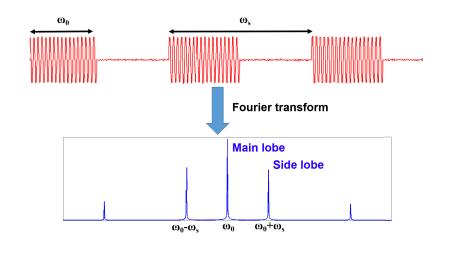

occurs. According to Fig.2.24, the continuous output microwave is cutoff intermittently. Refer to Fig.2.26, we will explain the sampling theorem with quantitative analysis. Generally, continuous microwave's Fourier transform is given as follows:

$$F(\omega) = \pi(\delta(\omega - \omega_0) + \delta(\omega + \omega_0)$$

(2.25)

Here, the  $\omega_0$  is frequency of microwave. And the microwave which is cutoff intermittently can be seen as sampling microwave using square function. The frequency of square function is sampling frequency ( $\omega_s$ ) and function can be presented as (2.26). Here,  $f_s(t)$  is signal which has been sampled. f(t) is sampled function and s(t) is sampling function.

$$f_s(t) = f(t) \times s(t) \tag{2.26}$$

$$F_s(\omega) = \frac{1}{2\pi} F(\omega) \bigotimes S(\omega)$$

(2.27)

Fourier transform of function (2.26) is presented as (2.27). Then we set the sampling function to square function, and sampled function is microwave. The formula of (2.27) can be presented as follows:

$$F_{s}(\omega) = \frac{1}{2\pi} \times \frac{2\pi\tau}{T_{s}} \sum_{n=-\infty}^{\infty} Sa(\frac{n\omega_{s}\tau}{2})\delta(\omega - n\omega_{s}) \bigotimes F(j\omega)$$

(2.28)

$$F_s(\omega) = \frac{\tau}{T_s} \sum_{n=-\infty}^{\infty} Sa(\frac{n\omega_s \tau}{2}) F(j(\omega - n\omega_s)$$

(2.29)

$$F_s(\omega) = k \sum_{n=-\infty}^{\infty} Sa(kn\pi) F(j(\omega - n\omega_s))$$

(2.30)

FIGURE 2.26: Fourier transform of intermittent microwave

FIGURE 2.27: Main Lobe and Side Lobe vs. Duty Ratio

Here, the  $\tau$  is the width of sequence function and  $T_s$  is sampling frequency. The duty ratio can be present as  $\tau/T_s$ . Formula (2.28) shows that the frequency of main lobe should be  $\omega_0/2\pi$  when n = 0. The frequency of side lobe should shift by  $\pm \omega_s$  when when n = 1. If we set the duty ratio as k, the formula (2.29) can be written as (2.30). k decide the numbers of lobe before the first zero point. For example, we set the k = 50%, there is only one side lobe before the first zero point.

FIGURE 2.28: Measurement Duration Result

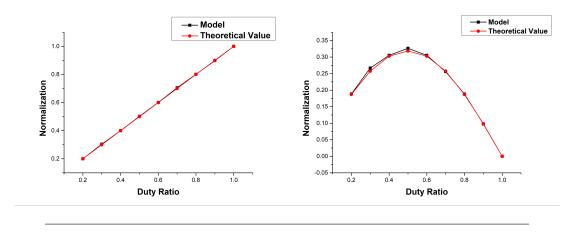

Then we do the mathematical model using the Matlab tools. The filter is set to chebyshev I type. We do Fourier transform to waveform presented at top of Fig.2.26. Besides, we add the thermal noise to simulate the circuits environment. The result is given at bottom of Fig.2.26. The waveform is match the expectation. The variation trend of main lobe and side lobe vs. duty ratio is presented at Fig.2.27. This model is almost the same with theoretical value. The main lobe is linear to duty ratio. The side

lobe is largest when duty ratio is 50%. That means when duty ratio is less than 50%, sampled signal does main favour. when duty ratio is beyond 50%, sampling frequency does main favour. The value of model is little bigger than theoretical value because of added thermal noise and designed filter model owns the decay.

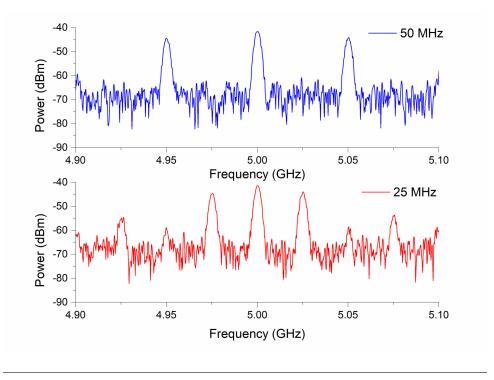

The measurement is presented at Fig.2.28. As analyzed before, if we set the duty ratio to 50%, there is only one side lobe before zero point. In this measurement, we keep the control current to constant (0.3  $\mu$ A). We present two examples which the sampling frequency is 50 MHz and 25 MHz. As figure shows, the sampling frequency can be revealed at side lobe. As fig.2.27 presented, the ratio of main lobe and side lobe is about 0.6 (*sidelobe/mainlobe*) when duty ratio is 50%. Signal power will decay by 0.36 and we transform it to power, which is about 4.43 dBm. That means the difference between main lobe and side lobe will arrive 4.43 dBm, where measurement value is near to this value.

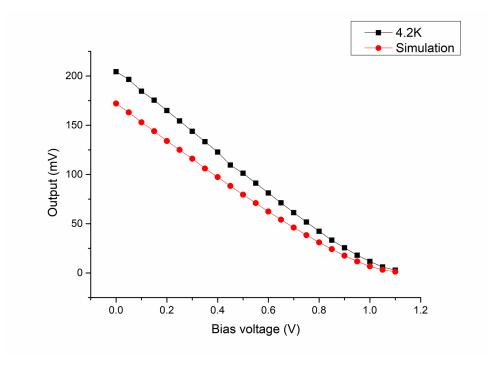

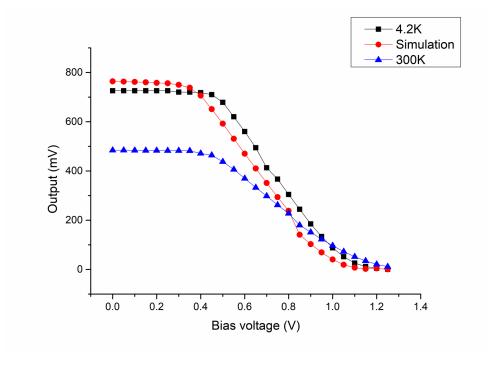

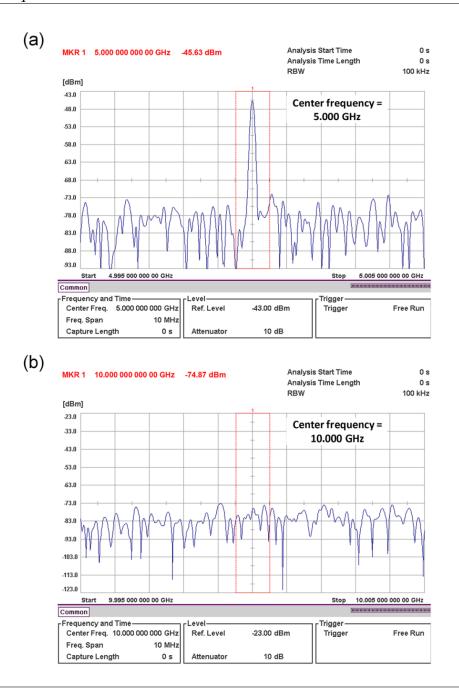

#### Amplitude Measurement Under High Speed

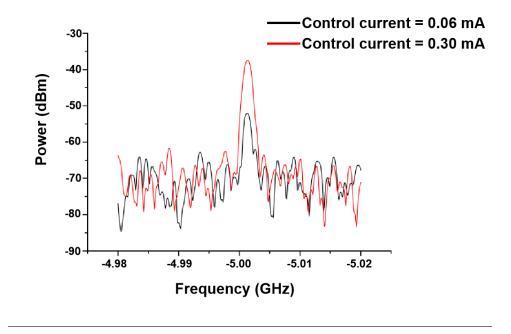

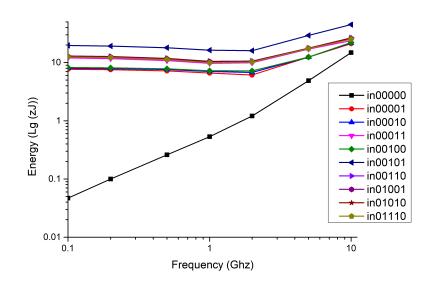

FIGURE 2.29: Measurement result with different control current

Fig.2.22 reveals the measurement process and here we remove the stop (blue) signal so that the output microwave will be continuous. The side lobe will be removed and we just need to change the control current (yellow) to change the amplitude of microwave. It is obvious that the amplitude of microwave will be revealed on the value of main lobe.

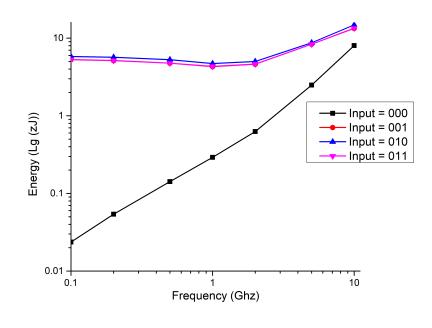

Here, we give the measurement result in Fig.2.29. The experimental instrument is spectrum analyzer. The amplitude change is very to be observed at oscilloscope because strong cross talk signal and thermal noise. Here, We amplify the signal (+38 dBm) and input to the analyzer. In this measurement we modulate the control current to present the value of main lobe. Fig. Fig.2.29 exhibits the experiment result. We scan the frequency from 4.9 GHz to 5.1 GHz and the main lobe is available at the 5 GHz because of TFF circuits. We set the control current to 0.3 mA and the main lobe is 38.67 dBm. The power is about 5.3 dBm larger than the signal which is sampled. It is close to theoretical value according to sampling theorem. Then we set the control current makes the pulses duration smaller. Thus, the amplitude value of microwave will be larger.

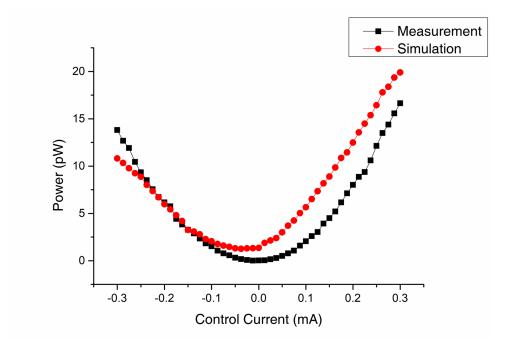

We make a summary of the output power and control current in Fig.2.30. We present output current and output power with the control current. The variation tendency shows a parabola type. The red line shows the measurement data and black line shows the simulation data. We simulate the output power consumption with load 50 ohm. We transform the measurement data by removing the enlargement factor, which present a parabola shape as well. The tendency between the simulation and measurement is resemblance. The data of simulation is little larger than that of the measurement when the control current is from 0 to 0.3 mA. It is due to the attenuation

| No. | Parameter name                         | Value            |  |

|-----|----------------------------------------|------------------|--|

| 1   | Margin of Bias current (Design)        | [-17% 15%µ]      |  |

| 2   | Margin of Bias current (100 kHz)       | [-15% 10%]       |  |

| 3   | Margin of Bias current (5 GHz)         | [-15% 4%]        |  |

| 4   | Range of Control Current (Design)      | [-3.2 mA 3.2 mA] |  |

| 5   | Range of Control Current (Measurement) | [-2.4 mA 2.4 mA] |  |

| 6   | Success rate of Measurement            | 4/5              |  |

TABLE 2.2: Circuits Margin of Measurement

excited in the measurement equipment (such as cables or probes). The result is not exactly symmetry because of the circuits parameter. Thus, the amplitude of output will be linear when control current is positive.

## 2.6 Conclusion

In conclusion, we suggest a variable amplitude microwave pulse generator circuits with superconducting circuits. We integrate the SFQ circuits and low pass filter on the chip and measurement at 4.2 K. We confirm the function of the circuits with low-speed signal at first. Then we apply the 10 GHz microwave to the MPG and the on-chip circuits can generate the 5 GHz output microwave. We observe the main lobe of the microwave in the spectrum analyzer when we modulate the control circuits. We confirm that input the larger control current, the system can generate larger microwave amplitude. At the control current range of 0 mA to 0.3 mA, the amplitude can achieve linear feature. Based on PPG system, it reveals the potential of controlling the microwave envelop if the control current can be controlled. What's more, we confirm the duration of microwave can be controlled according to the sampling theorem. It can be observed directly on the oscilloscope, however, the cross talk and noise have impact on it. The measurement result is given at Tab.2.2.

However, the control signal of this microwave generator is required from room temperature. To QEC system, the message from qubit should turn back to classic computer then feed back to microwave generator. To achieve the goal which is presented in Fig.1.3, we suggest to design a control system under cryogenic temperature with superconducting circuits or cryogenic circuits. The main targets for controlling are duration and control current.

## Chapter 3

# Timing Controller Circuits And Integrator Using AQFP

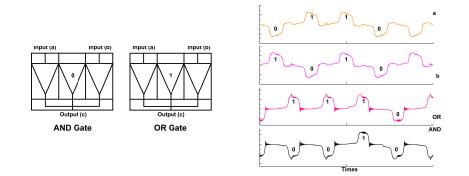

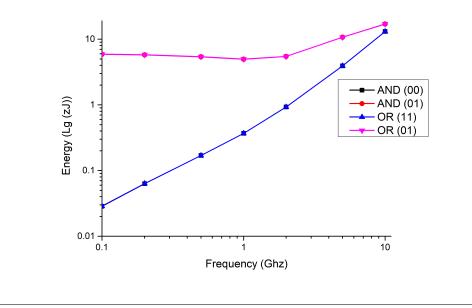

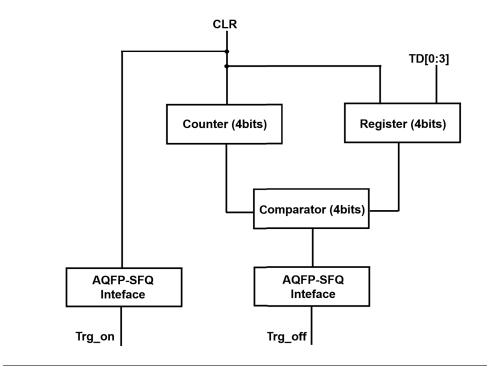

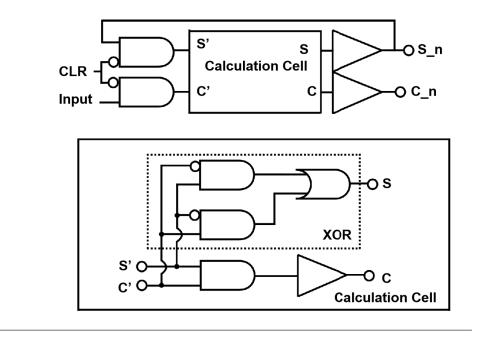

In this section we will introduce the timing controller and integrator circuits designed by Adiabatic Quantum Flux Parametron Circuit (AQFP). As mentioned, the quantum control and read-out system is required to implemented with cryogenic temperature. In the previous chapter, we introduce the microwave generator designed with SFQ circuits. However, the SFQ circuits owns a disadvantage is that it will cost lots of power on quiescent dissipation because it is required bias current all the time. DC-bias current will produce lots of thermal noise so that it will have impact on Quantum process especially under mK. The low power consumption should be applied. fortunately, the AQFP can take on it because it has no DC-bias current to junction. Therefore, we desired to design the controller with AQFP.

On the other hand, the state of qubit can be readout by Josephson parametric amplifier (JPA) or Josephson parametric oscillator (JPO). Thus, we can observe the phase shift to calculate qubit state and phase can be read out by AQFP circuits. To improve the sensitivity of readout system, we design the integrator using AQFP circuits. All the circuits structure and measurement result within 4.2 K will be presented in this chapter.

## 3.1 Adiabatic Quantum Flux Parametron (AQFP)

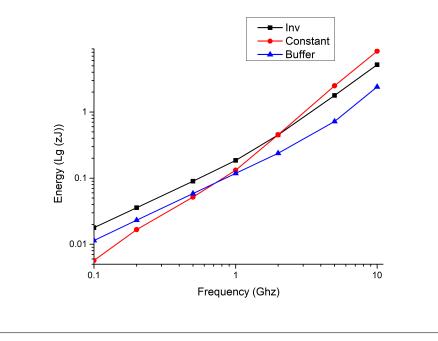

AQFP circuits can operate with energy dissipation close to the thermodynamic. Therefore, it can be an energy-efficient superconductor logic element based on the quantum flux parametron. There are many researches about AQFP have been reported and the logic cells designed by AQFP have been established. This section we will introduce the operation of AQFP and logic cell made by AQFP.

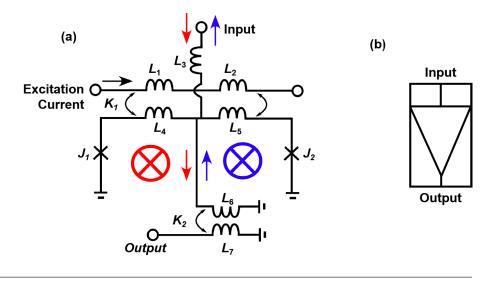

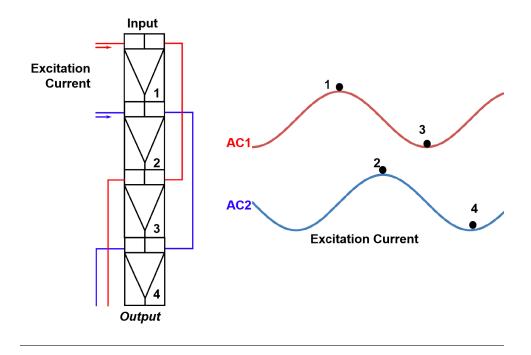

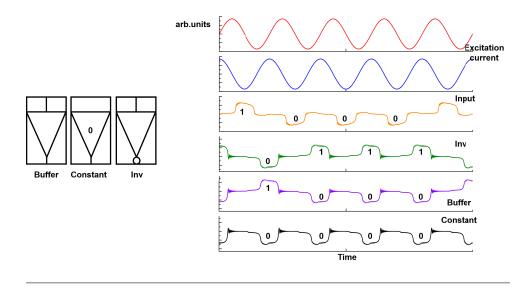

#### 3.1.1 Structure of AQFP

Here, we present the schematic of AQFP in Fig.3.1 (a). Excitation current is applied to add the external flux to the loop. The external current from  $L_1$  is added to  $L_4$  though coupling factor  $K_1$ . The loop left contains the  $J_1$ ,  $L_4$ ,  $L_6$  and loop right contains the  $J_2$ ,  $L_5$  and  $L_6$ . Assume that the structure is symmetrical and  $J_1 = J_2$ ,  $J_4 = J_5$ , the external flux which is from excitation current is the same to two loops. The flux cause the current is the opposite direction in inductance  $L_6$ . Thus, the loops function can be given as follows:

$$\phi_{J1} = \frac{2\pi L_6 I_6}{\Phi_0} - \frac{2\pi L_4 I_4}{\Phi_0} - 2\pi \frac{\Phi_{ex}}{\Phi_0}$$

(3.1)

$$\phi_{J2} = \frac{2\pi L_6 I_6}{\Phi_0} + \frac{2\pi L_5 I_5}{\Phi_0} + 2\pi \frac{\Phi_{ex}}{\Phi_0}$$

(3.2)

Here, we define the clockwise direction as positive current. The  $\Phi_{ex}$  is external flux. According to (3.1) and (3.2), the formula can be given as follows:

$$\phi_{J1} = -\frac{\pi L_5}{\Phi_0} (I_4 + I_5) - 2\pi \frac{\Phi_{ex}}{\Phi_0} - \frac{\pi L_4 I_{in}}{\Phi_0}$$

(3.3)

$$\phi_{J2} = -\frac{\pi L_5}{\Phi_0} (I_4 + I_5) - 2\pi \frac{\Phi_{ex}}{\Phi_0} + \frac{\pi L_4 I_{in}}{\Phi_0}$$

(3.4)

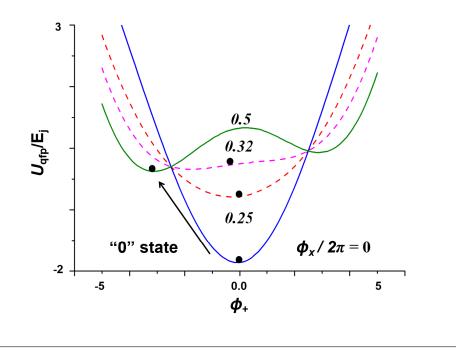

Here, we assume current  $I_in$  is input current and  $I_in = I_4 - I_5$ . The formula (3.3) and (3.4) reveals each JJ phases before switch. Once we input a external flux  $(0.5\Phi_0)$  the difference of JJ's phase will arrive more than  $2\pi$ . It means at least one JJ will switch. Formula (3.34) reveals that once the input current is positive (red arrow), phase of  $J_1$  will be beyond  $-\pi$ . The current on  $J_1$  be reversed and generate a flux which is opposite of the original flux (red cycle). On the other hand, if input current is negative (blue arrow), the phase of  $J_2$  will be beyond  $-\pi$  and generate a flux which is opposite of the original flux (blue cycle). Therefor, the message can be propagated using this principle. It can be seen as a buffer and symbol is presented in Fig.3.1.

FIGURE 3.1: Schematic of AQFP and symbol

Then we will explain it why it performs adiabatically. The potential energy of is behaved by the sum of the energy stored in  $J_1$ ,  $J_2$ ,  $L_4$ ,  $L_5$ , and  $L_6$ . The energy of  $J_1$  and  $J_2$  is presented as follows:

$$U_{j} = E_{j}(-\cos(\phi_{1} - \phi_{2})) = -2E_{j}\cos(\phi_{-})\cos(\phi_{+})$$

(3.5)

Here, the  $E_j = \frac{I_c \Phi_0}{2\pi}$ ,  $\phi_- = (\phi_1 - \phi_2)/2$ ,  $\phi_+ = (\phi_1 + \phi_2)/2$ .  $I_c$  is is the critical current of junction respectively. The energy in the  $L_6$  is given as follows:

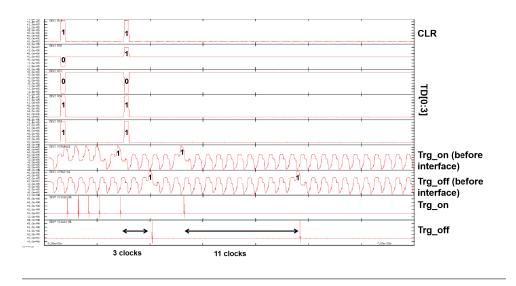

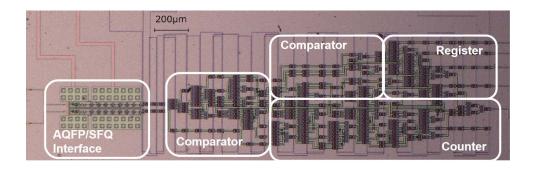

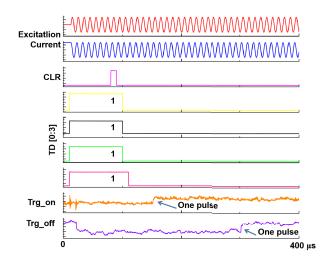

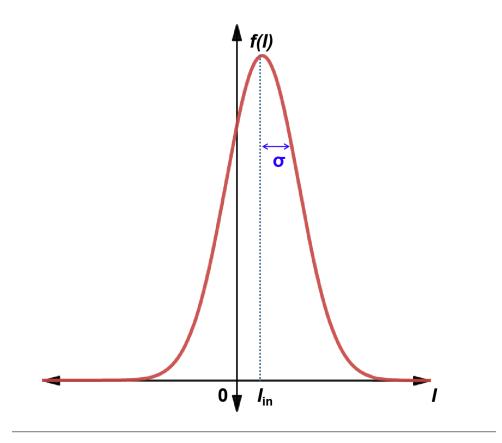

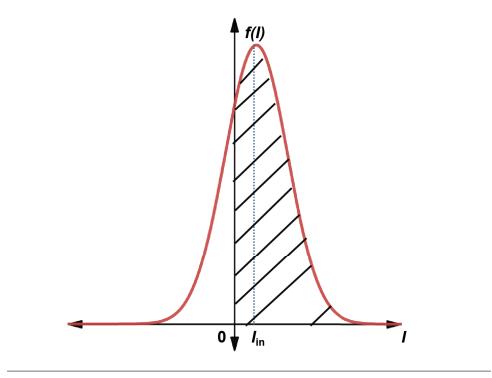

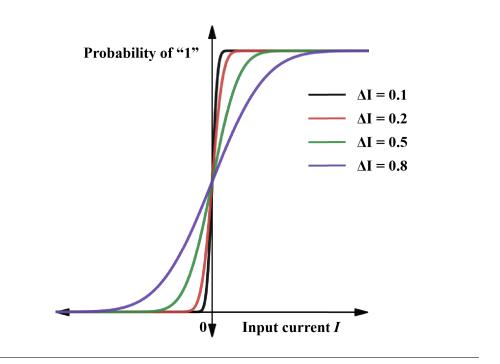

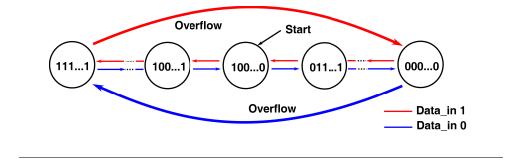

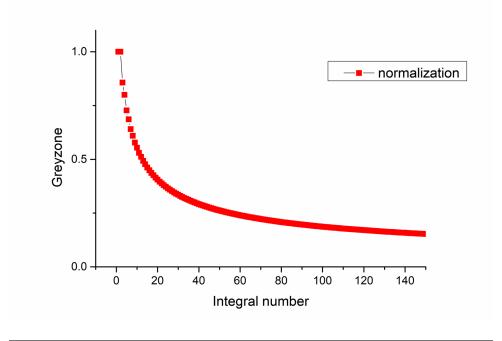

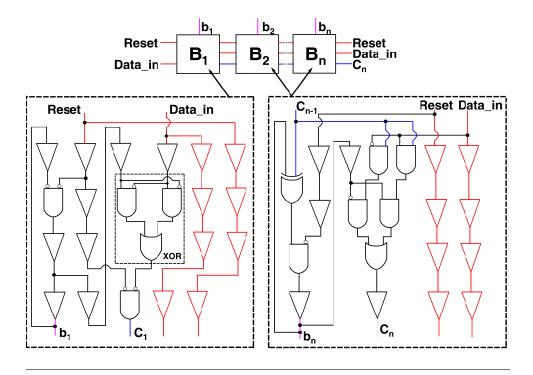

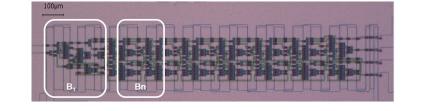

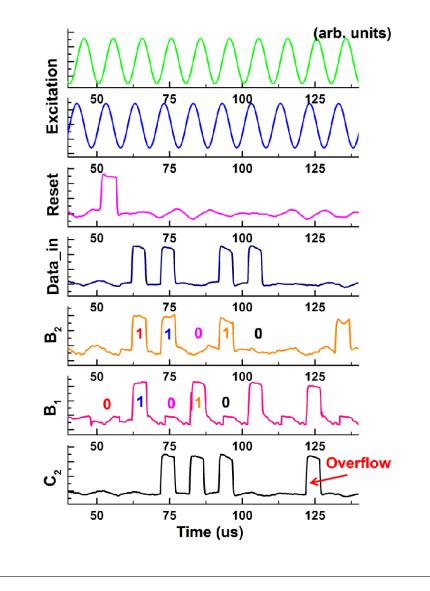

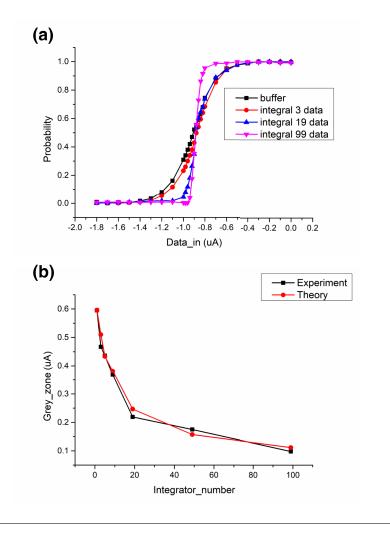

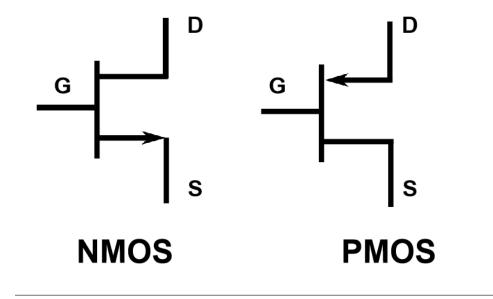

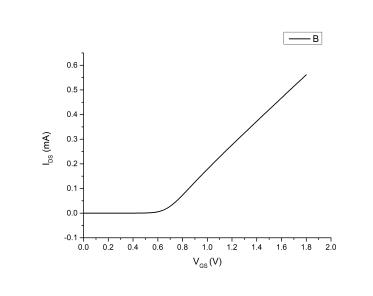

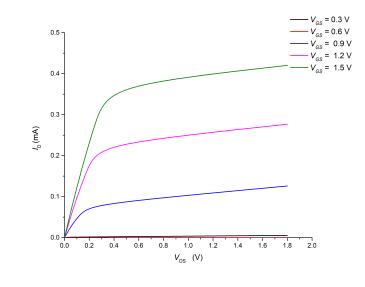

$$U_m = E_j \frac{\phi_q^2}{2\beta_q} \tag{3.6}$$