# 博士論文

# 大規模断熱量子磁束パラメトロン回路設計 法の研究

Study on the design methodology of large-scale adiabatic quantum-flux-parametron circuits

指導教官 吉川 信行教授

2023年3月10日

横浜国立大学 大学院理工学府 数物・電子情報系理工学専攻

20QC502 田中 智之 Tomoyuki Tanaka

## Abstract

The amount of data handled by humankind is increasing every year. The data center which provides services such as Internet commerce and video streaming services has a market share that is expected to increase by USD 615.96 billion from 2020 to 2025, and the market's growth momentum will accelerate at a compound annual growth rate (CAGR) of 21.98% [1]. This growth means that data centers will deploy many more computers, and one projection predicts that data centers will consume 8% of the earth's electricity in 2030 [2]. The information society faces the problem of power consumption.

CMOS circuits used in computers as arithmetic circuits have a problem with miniaturization. For example, TSMC, a leading foundry for logic circuits, has announced that it will begin mass production of N3 (3 nm) technology in the second half of 2022. However, given that the diameter of an atom is about 0.1 nm, it is clear that further miniaturization will be even more difficult. Computers with low power consumption and high performance are needed in the future. We have been working on the realization of next-generation computers, focusing on adiabatic quantum-flux-parametron (AQFP) circuits. A superconductor circuit is a device based on Josephson junctions, which can operate faster and consume much less power than CMOS circuits[3]. The AQFP circuit is an even more energy-efficient logic device among superconductor circuits, consuming 1/100,000 of the energy of CMOS[4, 5].

There are many hurdles to overcome one by one in order to put AQFP circuits into practical use. This thesis improves the design environment for AQFP circuits by addressing the application of variable-length wiring and methods to achieve the same level of the environment in AQFP circuits as in CMOS circuit design.

# Contents

| Chapter 1     | Intrduction                                                | 3  |  |

|---------------|------------------------------------------------------------|----|--|

| 1.1           | Limitation of CMOS based computer                          | 3  |  |

| 1.2           | Increased demand for computing resources                   | 4  |  |

| 1.3           | Superconductor post-CMOS computing                         | 6  |  |

| 1.4           | Structure of this paper                                    | 8  |  |

| Chapter 2     | Theory of adiabatic quantum-flux-parametron                | 9  |  |

| 2.1           | Introduction                                               | 9  |  |

| 2.2           | Potential energy of AQFP circuit                           | 9  |  |

| 2.3           | Data propagation of AQFP circuits                          | 13 |  |

| 2.4           | Excitation of AQFP circuit                                 | 13 |  |

| 2.5           | Logic circuit using the AQFP circuit                       | 16 |  |

| Chapter 3     | RTL to GDS flow for large AQFP circuits                    | 27 |  |

| 3.1           | Introduction                                               | 27 |  |

| 3.2           | Full-custom environment setup and cell library development | 27 |  |

| 3.3           | AQFP RTL-to-GDS flow                                       | 30 |  |

| 3.4           | Conclusion                                                 | 37 |  |

| Chapter 4     | Channel routing for AQFP circuits                          | 39 |  |

| 4.1           | Routing structure of AQFP cirucits                         | 39 |  |

| 4.2           | Channel routing optimization with Glitter                  | 46 |  |

| 4.3           | Glitter, variable-width channel router                     | 46 |  |

| 4.4           | Conclusion                                                 | 51 |  |

| Chapter 5     | Ciruit design and test                                     | 53 |  |

| 5.1           | Adder(Kogge-Stone adder)                                   | 53 |  |

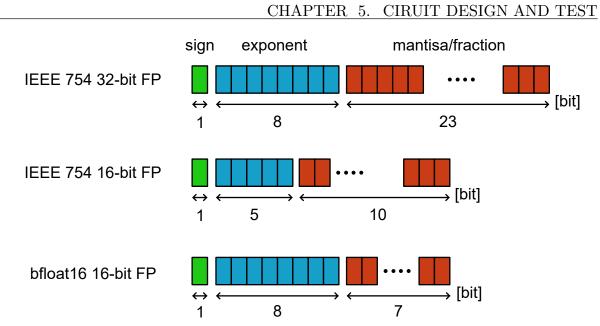

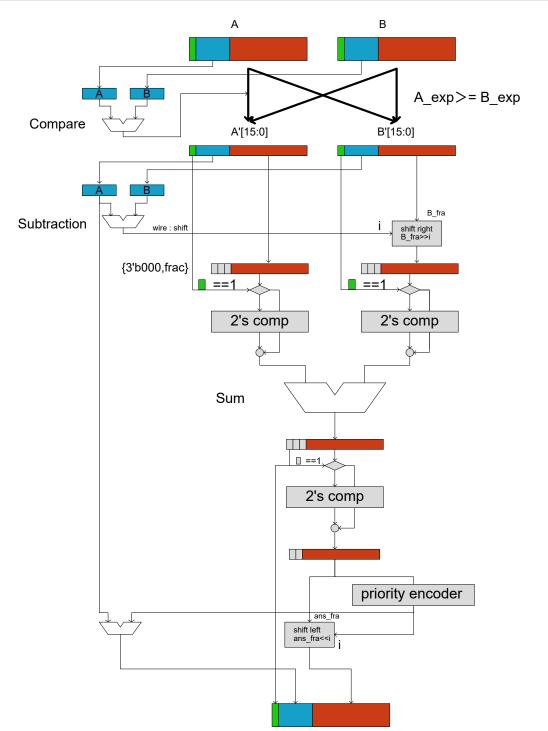

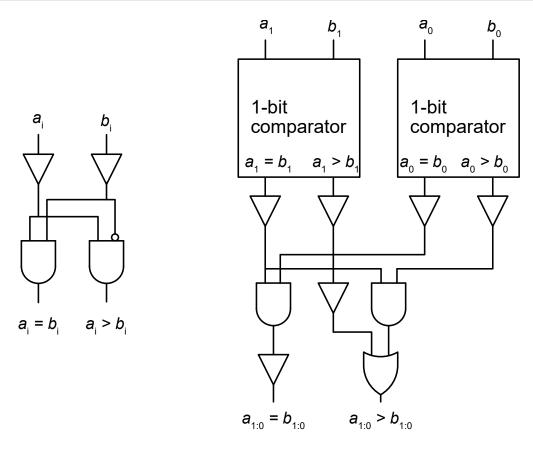

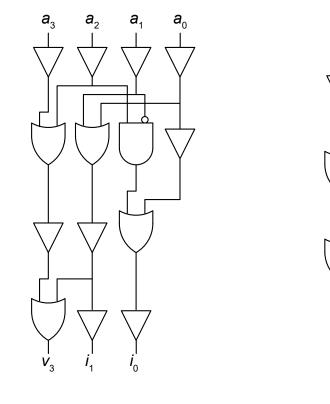

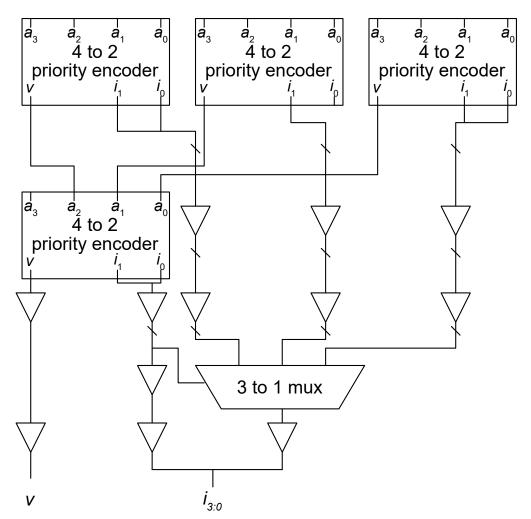

| 5.2           | bfloat 16 floating point adder                             | 69 |  |

| 5.3           | Conclusion                                                 | 77 |  |

| Chapter 6     | Conclusion                                                 | 79 |  |

| Acknowledgeme | ents                                                       | 81 |  |

| Appendix A    | Synthesis results                                          | 83 |  |

| 本研究に関する       | 本研究に関する発表                                                  |    |  |

## Bibliography

105

# Chapter 1

# Intrduction

## 1.1 Limitation of CMOS based computer

Computers are the infrastructure of human life. Computers control everything and anything, and they have become so important that many people might lose their lives if they suddenly become unable to use computers. Since the invention of the transistor, complementary metal oxide semiconductor-based computers (CMOS) have experienced explosive growth and have contributed significantly to the advancement of human society.

CMOS will soon face a miniaturization problem. The most advanced process rules have reached around 3 nm in 2022, and the leading research laboratory of semiconductors; Interuniversity Microelectronics Centre(imec) claims it will be possible to get 0.2 nm by 2040[6]. Since the atomic radius of silicon and metals used in wiring is about 0.1 nm, the process rule cannot be smaller than 0.1 nm due to physical limitation. This limitation means that semiconductor growth will stagnate in 2040, after which computers may be left to structures that are not CMOS. In other words, near 2040, we will face a problem with the stagnation of providing calculation resources.

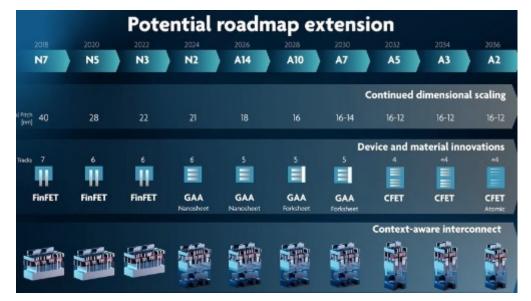

Figure 1.1: Loadmap of miniaturization of CMOS transistor[6]. They said the process rule of state-of-the-art CMOS will reach 0.2 nm in the 2040s.

# 1.2 Increased demand for computing resources

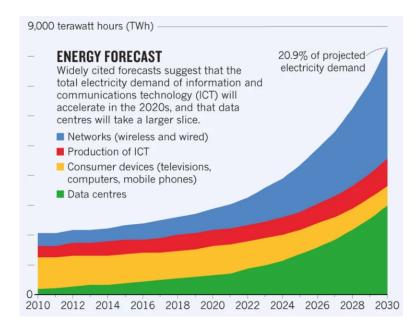

Think about the projections for the demand for computing resources: the metaverse with virtual reality and mixed reality, the Internet of things where various devices are connected to the Internet, on-demand video streaming such as Youtube and Netflix, etc. It is not difficult to believe that the demand for computing is only going to increase. Indeed, according to an article reported in Nature in 2018, networks and computers are expected to use 20% of the electricity consumed on the planet in the 2030s, and the increase in computers is considered one of the major obstacles to decarbonization, which is the current trend[2].

Figure 1.2: Projected power consumption by information and communication devices, which around 2022 was about 10% of total power consumption, but is expected to exceed 20% around 2030[2]. In particular, the infrastructure side, namely networks and data centers, will increase dramatically.

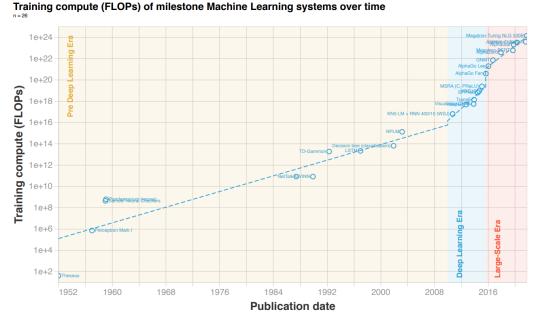

Figure 1.3: A graph showing the increase in learning models, which had been gradually increasing since around 1950, but increased dramatically after 2010. No sign of stagnation in the increase can be observed[7].

Further progress is also needed in terms of computer quality. One application that uses large amounts of computing resources is machine learning. Examples of applications include automated driving and chatbots. In particular, chatbots have made significant progress in recent years, but they are still in their infancy[8]. In order to improve performance, it is necessary to expand learning models. Already the pace of growth of learning models is extremely fast, doubling in size every six months since 2010, and there is no indication yet that this trend will slow down. There is a reason why the field of machine learning requires high-performance computers[7].

### 1.3 Superconductor post-CMOS computing

Superconductor circuits are a typical example of Post-CMOS circuits. It uses the Josephson junction as an active element for arithmetic operations and has excellent high-speed operation and low power consumption.

#### 1.3.1 Single flux quantum circuit

Single flux quantum (especially RSFQ) circuits are digital devices with excellent highspeed operation, and have been successfully demonstrated in 4-bit microprocessors. In addition, 8-bit microprocessor designs and component operation demonstrations are underway, mainly at Nagoya University and Kyushu University, and a complete 8bit microprocessor is nearing completion[9, 10]. The operating clock of this processor is 50 GHz, and power consumption is estimated to be 10<sup>13</sup> ops/W. The operation of a 32-bit arithmetic unit has been verified in simulations, and steady progress is being made toward practical application[11].

If the RSFQ circuit can be put to practical use, it would raise the clock frequency of computers by a factor of 10. This would be a great boon for applications where real-time performance is important, such as weather simulation for weather forecasting.

Unfortunately, however, even if RSFQ circuits are commercialized, decarbonization will not progress.

Superconducting circuits operate at cryogenic temperatures of around 4K, which means that the chips must be constantly cooled. Cooling from room temperature to operating temperature 300 K to 4.2 K requires an extra power consumption of around 400 W to 5000 W[3]. To make a fair comparison with a conventional computer operating at room temperature, this power needs to be added to the power consumption of the circuit.

The Green 500 is a contest for the lowest power consumption of supercomputers, and the winner of the Green 500 announced in the fall of 2022 was a supercomputer called "Henri" installed at the Flatiron Institute in the U.S., with the energy efficiency is 65.091 GFlops/W. The results already show that conventional computers are more energy efficient, although this is not a strict comparison because of the different bit widths and architectures[12].

SFQ circuits also have various innovations to reduce power consumption, but they have problems such as lowering the operating frequency, and SFQ circuits are not a silver bullet that can solve all the problems that computers face[13, 14].

#### 1.3.2 Adiabatic quantum-flux-parametron circuit

In order to balance the problem of increasing the amount of information handled by mankind with power savings, we need digital devices that can operate moderately faster than CMOS circuits and consume three or more orders of magnitude less power than that one. Adiabatic quantum-flux-parametron (AQFP) circuits are an alternative circuit technology to CMOS circuits. AQFP circuits are superconductor circuits that operate at5 GHz to 10 GHz and consume 5 to 6 orders of magnitude less power than CMOS circuits at the same operating frequency[5].

Previously, the AQFP, a 4-bit microprocessor, MANA, was demonstrated in operation[15]. This processor was designed to operate at 5 GHz and consumed  $3.2 \times 10^{13}$  ops/W. To compare this circuit to the RSFQ circuit, it is extended to 8-bit width. Even if the power consumption were increased by a factor of 8 in the pessimistic scenario, the power consumption would still be  $4 \times 10^{12}$  ops/W. The CMOS, RSFQ, and AQFP circuits are compared in table 1.1. Even with rough reasoning, the AQFP circuit can consume up to 100 times less power than the CMOS circuit. In addition, AQFP can operate at up to 10 GHz, which is slow compared to RSFQ circuits, but fast enough compared to current CMOS circuits. In other words, if a computer can be realized using AQFP circuits, the two immediate problems of insufficient computing resources and increased power consumption can be solved.

|           | Clock frequency                                  | Efficiency at $300\mathrm{K}$          | The architecture |

|-----------|--------------------------------------------------|----------------------------------------|------------------|

| CMOS[12]  | $5\mathrm{GHz}$                                  | $6.5 \times 10^{10}  \mathrm{Flops/W}$ | 64-bit           |

| RSFQ[9]   | $50\mathrm{GHz}$                                 | $10^{10}\mathrm{ops/W}$                | soon $8$ -bit    |

| AQFP [15] | $5\mathrm{GHz}\ (\mathrm{max.}\ 10\mathrm{GHz})$ | $4 \times 10^{12} \mathrm{ops/W}$      | 4-bit            |

Table 1.1: Comparison of the architecture of digital device

Basic research on how to drive AQFP circuits and investigation of power consumption has progressed to date, and the next step is to work toward more practical applications. Practical circuits will need to be 10 or 100 times larger than the circuits designed to date, requiring ingenuity in circuit design and software development.

#### 1.3.3 Purpose of this research

The current state of research on AQFP circuits is limited to a small scale compared to RSFQ circuits. This is due to the fact that most of the circuit design needs to be done manually, which requires a long time to design, and because of this, it is difficult to optimize the circuit structure. There have been several studies to improve the efficiency of designing AQFP circuits, but the main focus is on logic synthesis to optimize the graph of the circuit. While this is an important task because graph optimization reduces the area and latency of the circuit, it is more important to generate the physical circuit. Therefore, this study addressed both the routing and placement of AQFP circuits.

## 1.4 Structure of this paper

This paper consists of three major parts. The first part explains the basic theory of superconducting circuits and the principle of operation of AQFP circuits. Next, it describes the design flow of the AQFP circuit, and finally, it describes the actual circuit's design and measurement results. Chapter 2 explains the basic theory of AQFP and how to design the circuit. Chapter 4 explains to alleviate the limitation of the data propagation length limit of the AQFP circuit by introducing variable wiring height. Chapter 3 describes the automatic design of circuits similar to CMOS circuits to improve the design capability of AQFP circuits dramatically.Chapter 5 reports on the design and operational demonstration of AQFP integer and floating-point adders using the methods proposed in chapters 3 and 4 for designing large AQFP circuits. Chapter 6 reports a summary of the contents of this thesis.

# Chapter 2

# Theory of adiabatic quantum-flux-parametron

#### 2.1 Introduction

This chapter first provides an overview of adiabatic quantum-flux-parametron (AQFP) circuits and their principle of operation. Then, how the AQFP circuit defines the binary information of '0' and '1' is explained, and the circuit design procedure is described.

Goto et al. at the University of Tokyo developed the quantum-flux-parametron circuit (QFP) in 1985. It can operate at several GHz and has one of the lowest power consumption among superconductor circuits. They have demonstrated the operation of an analog-to-digital converter operating at 18 GHz, high-speed operation at 36 GHz, and the design and operational implementation of an arithmetic logic unit (ALU) [16, 17, 18].

We are investigating adiabatic quantum-flux-parametron (AQFP) circuits, which operate adiabatically in QFP circuits. AQFP circuits have no static power consumption because they are driven by AC flux bias, and their dynamic power consumption is minimized because the potential of the circuit changes adiabatically.

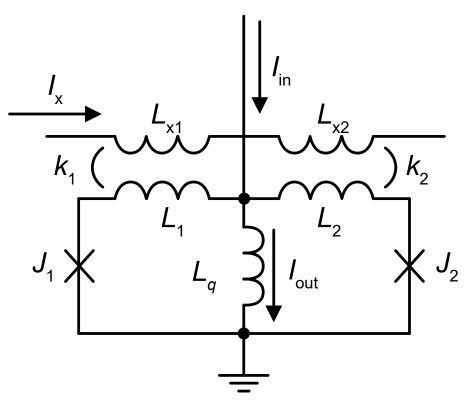

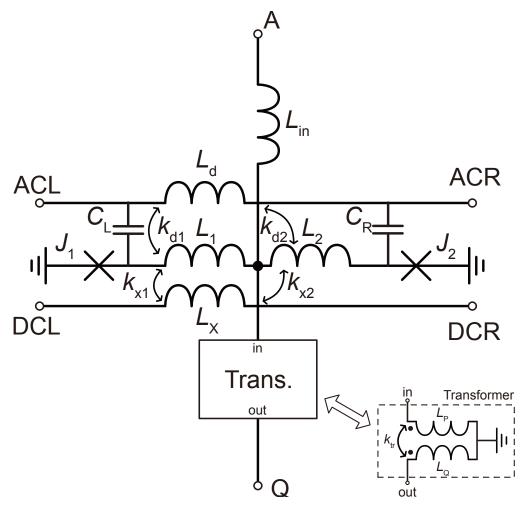

Figure 2.1 shows the schematic of the AQFP circuit, in which the Josephson junction of the RF-SQUID is replaced by a DC-SQUID. The circuit parameters are symmetrical. In addition, since there are no resistors in the circuit, static power consumption is not generated.

## 2.2 Potential energy of AQFP circuit

In this section, the potential energy of the QFP circuit is explained. figure 2.1 shows the circuit diagram of a QFP circuit, and assuming these relationships  $L_{x1} = L_{x2} = L_x$ ,  $L_1 = L_2 = L$ ,  $k_1 = k_2$ ,  $J_1 = J_2$  that the QFP circuit has a symmetrical structure, euqation (2.1) shows the potential energy[19, 20].

Figure 2.1: Schematic of AQFP circuit. It consists of two superconductive loops with Josephson junctions (x mark in the figure). In addition, unlike RSFQ circuits, for example, there is no static power consumption because the circuit has no resistance.

$$U = E\left[\frac{(\phi_{\rm x} - \phi_{-})^2}{\beta_{\rm L}} + \frac{(\phi_{\rm in} - \phi_{+})^2}{\beta_{\rm L}}2\beta_{\rm q} - 2\cos\phi_{-}\cos\phi_{+}\right]$$

(2.1)

$$E = \frac{I_c \Phi_0}{2\pi} \tag{2.2}$$

$$\phi_{\rm x} = 2\pi \frac{k\sqrt{LL_{\rm x}}I_{\rm x}}{\Phi_0} \tag{2.3}$$

$$\phi_{\rm in} = 2\pi \frac{L_{\rm x} L_{\rm in}}{\Phi_0} \tag{2.4}$$

$$\phi_{+} = \frac{\phi_1 + \phi_2}{2} \tag{2.5}$$

$$\phi_{-} = \frac{\phi_{1} - \phi_{2}}{2} \tag{2.6}$$

$$\beta_{\rm L} = 2\pi \frac{LI_{\rm c}}{\Phi_0} \tag{2.7}$$

$$\beta_{\rm q} = 2\pi \frac{L_{\rm q} I_{\rm c}}{\Phi_0} \tag{2.8}$$

$I_{\rm c}$  is the critical current value of  $J_1, J_2$ , and  $\phi_1, \phi_2$  are the phase difference of  $J_1, J_2$ ,

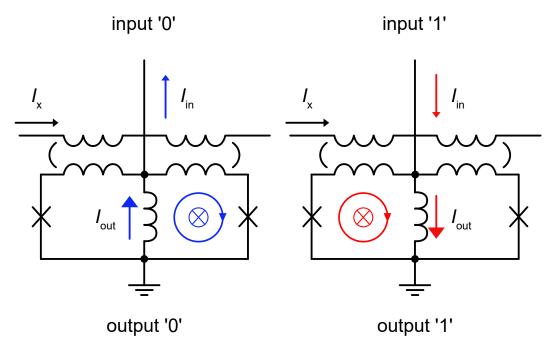

(a) The logic state is '0'.

(b) The logic state is '1'.

Figure 2.2: Two states of the AQFP circuits. When the current of the center inductance of AQFP flows upwards, this is state "0". If the current flows downwards, it is state "1".

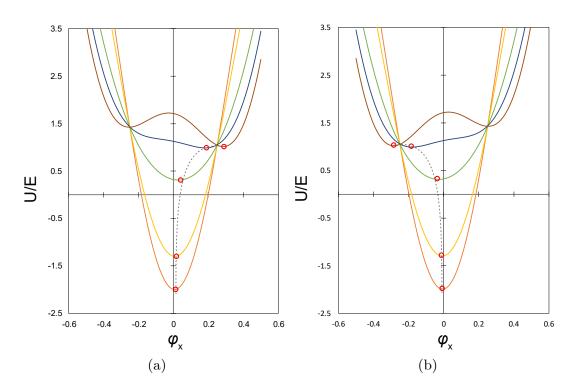

Figure 2.3: The figure shows the potential change of the AQFP circuit. The trajectory of the potential is shown by red dots and dashed lines. (a) corresponds to a positive input current and (b) corresponds to a negative input current.

respectively.  $\beta_{\rm L}, \beta_{\rm q}$  denote the normalized inductance  $L, L_{\rm q}$ , respectively. And assuming  $\phi_{-} = \phi_{\rm x}$ , equation (2.1) is changed as follow.

$$\frac{U}{E} = \left[\frac{(\phi_{\rm in} - \phi_{+})^2}{\beta_{\rm L} + 2\beta_{\rm q}} - 2\cos\phi_{\rm x}\cos\phi_{+}\right]$$

(2.9)

This equation is plotted graphically in figure 2.3. In the initial state,  $I_x = 0$ , i.e.,  $\Phi_x = 0$ , the potential of the circuit has a single-well structure. When  $I_x$  is increased, the cosine term in the potential becomes dominant, and the structural changes to a double-well structure. Whether the minimum point of the potential takes a right or left is uniquely determined by the polarity of the current in  $\Phi_{in}$  given as the signal input. When the potential tilts to the right, as in Figure figure 2.3(A), it means state "0", and when the potential tilts to the left, as in figure 2.3(B), it means state "1".

Energy dissipation of the AQFP during the clocking cycle  $E_{sw}$  is described below.

$$E_{\rm sw} \simeq 2I_{\rm c} \Phi_0 \frac{\tau_{\rm j}}{\tau_{\rm x}} \tag{2.10}$$

$$\tau_{\rm j} \simeq 2\pi \frac{L_{\rm j}}{R} = \frac{\Phi_0}{I_{\rm c}R} = \sqrt{\frac{2\pi\Phi_0 C_{\rm s}}{\beta_{\rm c}J_{\rm c}}} \tag{2.11}$$

$$L_{\rm j} = \frac{\Phi_0}{2\pi I_{\rm c}} \tag{2.12}$$

$$\beta_{\rm c} = Q^2 = \frac{2\pi R^2 C I_{\rm c}}{\Phi_0} \tag{2.13}$$

$$E_{\rm sw} \simeq \frac{2\Phi_0^2}{R\tau_{\rm x}} \tag{2.14}$$

$L_{\rm j}$ , R,  $C_{\rm s}$ , C,  $J_{\rm c}$  and  $\beta_{\rm c}$  are Josephson inductance, the equivalent resistance of the subgap resistance and shunt resistor, junction capacitance per area, junction capacitance, the critical current density and McCumber parameter[21], respectively.  $\tau_{\rm x}$  is the duration time of the switching process and  $\tau_{\rm j}$  is the time constant that comes from the characteristic of Josephson junctions. As can be seen from the equations (2.10), (2.11) and (2.14), power consumption can be reduced by flowing modification.

- Using high- $J_c$  fabrication process.

- Using high- $\beta_c$  Josephson junctions. In other words, to use unshunted JJ (to increase shunt resistance).

The typical energy dissipation of AQFP is  $E_{\rm sw} \simeq 10 \times 10^{-19}$  J for  $I_{\rm c} = 25 \,\mu\text{A}$ ,  $C = 1 \,\mathrm{pF}$ ,  $R = 1 \,\Omega[22]$ . The combination of  $\beta_{\rm L}$  and B determines the adiabatic change in the potential of the circuit. Decreasing  $\beta_{\rm L}$  and  $\beta_{\rm q}$  decreases the energy consumed. Also, decreasing  $\beta_{\rm L}$  and increasing  $\beta_{\rm q}$  increases the operating margin of the circuit for the excitation current. There is a trade-off between the operating margin of the circuit and the energy consumption, and the value of  $\beta_{\rm q}$  determines it. For the AQFP circuit in the AIST HSTP process, a combination of  $\beta_{\rm L}$  and  $\beta_{\rm q}$  of 0.2 and 1.6 is used.

## 2.3 Data propagation of AQFP circuits

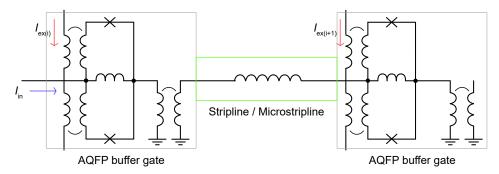

Microstrip or strip lines are used for signal propagation in the AQFP circuit. The circuit diagram is shown in figure 2.4. The AQFP circuit has a transformer in the output of the signal current. Since the binary of the AQFP circuit is determined by the polarity of the current, reversing the coupling direction of the transformer allows for NOT operation without additional implementation cost. When the buffer gate switches, a quantum magnetic flux  $\Phi_0 = 2.067851 \times 10^{-15}$  Wb penetrates the superconducting loop. A circulating current flows through the loop to counteract the magnetic flux, and the current is determined by  $I_{\text{loop}} = \Phi_0/L[A]$ . Since the coupling coefficient of the transformer is about  $k \simeq 0.5$ , the current flowing in the superconducting loop including the signal line is  $I_{\text{signal}} \simeq 0.5\Phi_0/L_{\text{stripline}}[A]$ . The input current to the gate  $I_{\text{signal}}$  must be sufficiently larger than the gray zone of the AQFP buffer gate. The minimum required current has been studied based on simulation and measurement results, and it is assumed to be  $I_{\text{th}} = 7 \,\mu\text{A}$ . Considering the standard microstrip lines in use, the wiring length is about 1000  $\mu\text{m}$ .

Figure 2.4: Signal propagation of AQFP circuit. The AQFP buffer gate contains a transformer, and the output current of the buffer gate propagates the signal through the transformer and stripline or microstrip line to the next gate. The inductance of the superconducting loop determines the current flowing in the signal line.

## 2.4 Excitation of AQFP circuit

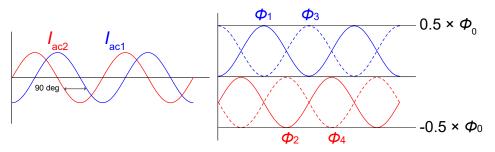

AQFP circuits can be operated by applying a periodic current, and the current waveform can be sinusoidal, square, or triangular. However, since AQFP circuits can reduce power consumption by slowing the switching process, providing discontinuous waveforms will increase power consumption. Therefore, a sine wave is usually used to excite the circuit. A three-phase excitation scheme was first proposed, in which the phase difference between the excitation currents applied to the sending gate and the receiving gate is  $120^{\circ}$ . Then, it is followed by a four-phase excitation scheme in which the phase difference is  $90^{\circ}[23]$ . The four-phase excitation method has a broader timing margin of the circuit, and the stability of the circuit at high-speed operation is improved. There are also proposals for 8- and 12-phase excitation schemes and delay

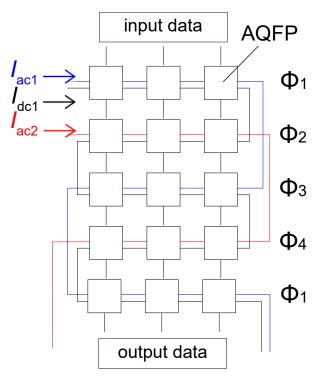

Figure 2.5: Diagram of the circuit configuration for the 4-phase excitation scheme of the AQFP circuit. There are three excitation currents are wired in meander form from left to right. The DC current is wired sequentially from the top to bottom, and the AC currents are wired from top to bottom by skipping one phase in sequence. As shown in figure 2.6, the two currents have a phase difference of  $1/2\pi$ . The interaction of the AC and DC currents flow directions excites the circuit four times per cycle. Therefore, the *i*-th and (i + 4)-th gates from the top are excited at the same time.

line clock, which uses on-chip delay lines to create a phase difference [24, 25]. However, unless otherwise noted, this paper will focus on the 4-phase excitation scheme. Figures 2.5 and 2.6 shows 4-phase clocking scheme and placement of the gate.

Figure 2.6: A method of creating four phase differences by the interaction of DC and AC currents. The magnitude of the three currents is equivalent to  $1/4\phi_0$ , and the two AC currents have a phase difference of  $1/2\pi$ . The DC current is used to provide an offset to the AC current, and when wired as shown in figure 2.5, the AC and DC currents are positively biased when they are in the same direction and negatively biased when they are in opposite directions. Since the AQFP circuit has no polarity, the circuit switches when the total input current exceeds  $\pm 1/2\phi_0$ , so wiring it as shown in the figure can create four phase differences.

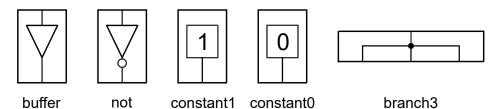

Figure 2.7: Basic symbols for AQFP circuits. From left to right: buffer, not, constant0, constant1 and branch3. Branch circuits have different numbers of branches, branches 2, 3, 4, and 5.

## 2.5 Logic circuit using the AQFP circuit

#### 2.5.1 Basic cells of AQFP logic circuits

The AQFP circuit has four basic gates [26]. The respective circuit symbols are shown in figure 2.7.

- buffer Figure 2.1 shows schematic of buffer gate. When the circuit is excited, a current in the same direction as the input current is generated. Since the gate does not perform logic operations, it is used to synchronize signal timing or to amplify current for long-distance propagation.

- **not(invert)** In figure 2.4, the circuit with a negative coupling coefficient for the output transformer is the inverter gate. A current in the opposite direction of the input current is generated.

- constant A gate with no input terminals, only output terminals. A gate in which the loop inductance of the superconducting loop is asymmetric, biasing the ease of switching the left and right Josephson junctions. The const0 gate and the const1 gate are mirror images of each other.

- branch A gate for splitting and merging currents. It is used to create branching and majority gates as described below.

The majority gate is used as basic gates for operations in AQFP circuits. A majority gate is a logic circuit that has 2n + 1 fan-in and 1 fan-out. It is a gate that outputs "0" when n + 1 inputs are "0" and outputs "1" when n + 1 inputs are "1" and outputs the one with the higher number of logic inputs. So far, 3-input, 1-output and 5-input, 1-output majority logic gates have been designed and included in the cell library [27]. Logic equations of the 3-input majority gate and the 5-input majority gates are shown in euqation (2.15) and euqation (2.16), respectively.

$$Maj(a, b, c) = ab + bc + ca$$

$$Maj(a, b, c, d, e) = abc + abd + abe + acd + ace + ade + bcd + bce + bde + cde$$

$$(2.15)$$

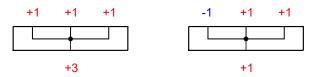

The principle of operation of majority logic gates is explained qualitatively: a three-

input majority logic gate has a structure that uses branch3 to join the outputs of three buffer gates. As shown in the figure, when a 3-input majority logic gate receives inputs {"0", "1", "1"}, the AQFP circuit assigns the logic state to the direction of current flow, so the direction of the output current is "1" according to Kirchhoff's law. A 5-input majority logic gate works in the same way by using a 5-input branch cell.

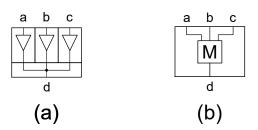

In principle, a majority gate can be created using only a branch circuit, since the current merging is used for the calculation. However, since the input current is determined by the magnitude of the wiring inductance, it is difficult to match the amount of current. For this reason, the majority logic gate in the cell library has a buffer gate attached to the input section to align the input current level. figure 2.9 shows a block diagram of a majority logic gate and its symbol.

Figure 2.8: Inside the majority logic gate, currents are merged, which represents majority logic. "-1" means upward current and "1" means downward current.

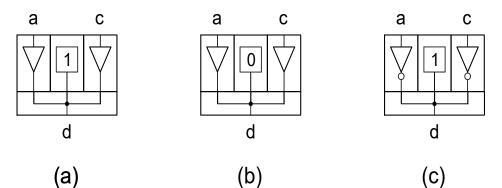

As can be seen from equation (2.15), the majority logic gate is a combination of AND and OR operations. By performing conversions such as those in equations (2.17) to (2.19), they can be used as majority logic gates AND, OR, and NOR gates. figure 2.10 shows schematic of each gates.

AND:

$$a \cdot 0 + 0 \cdot c + ca = ac \qquad (2.17)$$

OR:

$$a \cdot 1 + 1 \cdot c + ca = a + c$$

(2.18)

NOR:

$$\neg a \cdot 1 + 1 \cdot \neg c + \neg a \neg c = \neg a \neg c = \neg (a + c)$$

(2.19)

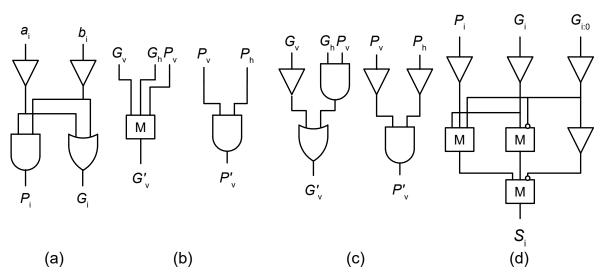

Figure 2.9: (a)Block diagram of a 3-input majority logic gate. buffer is attached to the input of the branch block to align the magnitudes of the input currents. Since the magnitude of the output current of the buffer and the not gate is equal, the majority logic operations with negative inputs are also possible by installing a not gate instead of a buffer gate. (b) Symbol of 3 input majority gate

Figure 2.10: Schematic of (a) OR gate, (b)AND gate, and (c) NOR gate. Equations (2.17) to (2.19) bring these conversions. The gate placed center in the schematic is the constant output gate.

#### 2.5.2 Energy dissipation of AQFP logic gate

Evaluating the energy consumption of AQFP circuits is more difficult than for RSFQ or CMOS circuits. This is because AQFP circuits do not have static power consumption, and because it is an adiabatic circuit, all energy received by the circuit is not dissipated during the calculation. The power consumption of an AQFP buffer gate  $E_{AQFP}$  is calculated by the following equation, where  $I_L(t)$  is the current in the excitation line,  $V_L(t)$  is the potential difference of the excitation line, and f is the operating frequency.

$$E_{\rm AQFP} = \int_0^{\frac{2\pi}{f}} I_{\rm L}(t) \times V_{\rm L}(t) dt \qquad (2.20)$$

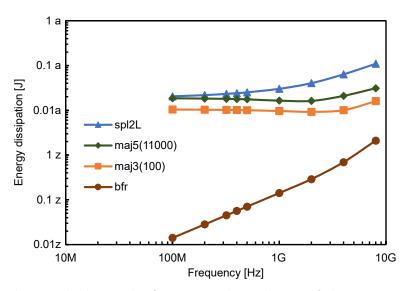

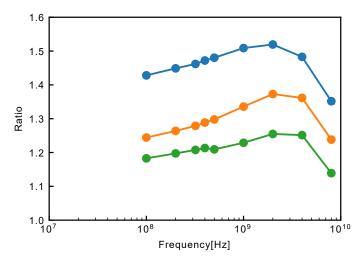

As shown in the figure 2.11, the power consumption of the AQFP buffer gate is proportional to the frequency, and the power consumption is zero when the circuit is excited using infinite time. The majority gate used for logic operations is energy saturated because any buffer whose input direction differs from that of another buffer causes that buffer to operate non-adiabatically. The most power-hungry gate is spl2L, a branch cell using a Josephson junction with a critical current of  $100 \,\mu\text{A}$ .

Figure 2.11: The graph shows the frequency dependence of the power consumption of the AQFP circuit. The energy consumption of the AQFP buffer gate is proportional to frequency. AQFP logic gates consume different amounts of energy depending on the input combination, and the combination with the largest energy consumption is shown as a representative example.

In the range above 5 GHz, energy consumption increases a little faster. This is due to the effect of plasma oscillations determined by the parameters of the Josephson junction. This effect is based on the AIST HSTP process and can be mitigated by using a process with a higher critical current density.

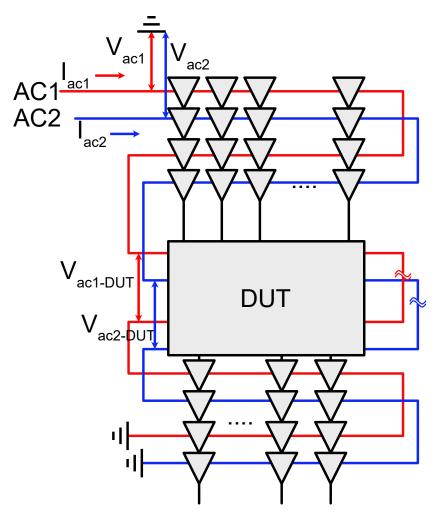

Evaluating the energy of gates that perform logic operations is a bit more complicated. This is because energy is exchanged between logic gates, and a method of evaluating energy that takes this effect into account is necessary. A systematic method has been proposed and is described below [28]. First, a somewhat long buffer chain is connected above and below the circuit to be measured and simulated, as shown in the figure 2.12. Total energy  $E_{tot}$  and consumed energy in the device under the test(DUT)  $E_{DUT}$  can be calculated in following equations.

$$E_{\rm tot} = E_{\rm ac1} + E_{\rm ac2} = \int W_{\rm ac1} + \int W_{\rm ac2}$$

(2.21)

$$E_{\rm DUT} = E_{\rm ac1-DUT} + E_{\rm ac2-DUT} = \int W_{\rm ac1-DUT} + \int W_{\rm ac2-DUT}$$

(2.22)

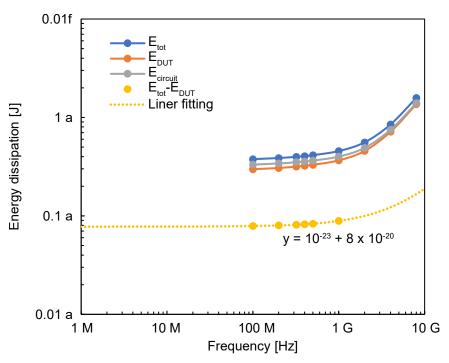

Then, to find a linear approximation function of  $E_{\text{diff}}$ , the difference of  $E_{\text{tot}} - E_{\text{DUT}}$ . The constant term of this function is the energy received by the DUT from the outside as signal current. Therefore, the energy consumed by the AQFP circuit,  $E_{\text{circuit}}$ , is  $E_{\text{circuit}}(f) = E_{\text{DUT}}(f) + E_{\text{diff}} + const$  Figure 2.13 shows curve of measured energy. The difference of energy  $E_{\text{diff}}$  becomes almost linear.

Figure 2.12: Circuit diagram for measuring the energy consumption of an AQFP circuit. A buffer chain is connected to the input and output ends of the Design Under Test (DUT), and the energy of the entire circuit and the energy consumed by the DUT are obtained from the simulation.

Figure 2.13: An example of how to calculate energy consumption. Calculate the energy consumed by the entire circuit,  $E_{tot}$ , and the energy consumed by the DUT,  $E_{DUT}$ , and then find the difference between  $E_{tot}$  and  $E_{DUT}$ ,  $E_{diff}$ . Since the constant term in the linear approximation of  $E_{diff}$  is the energy received and consumed by the DUT from sources other than the excitation line, the sum of  $E_{DUT}$  and the constant term is the energy consumed by the circuit,  $E_{circuit}$ .

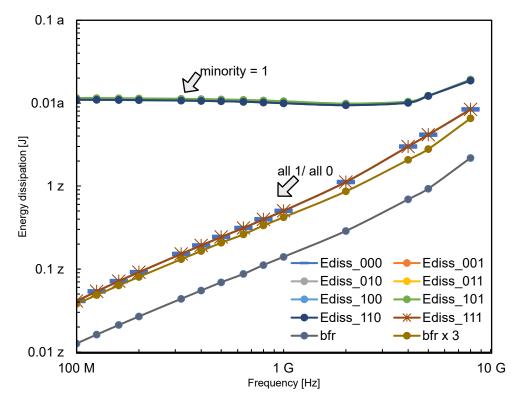

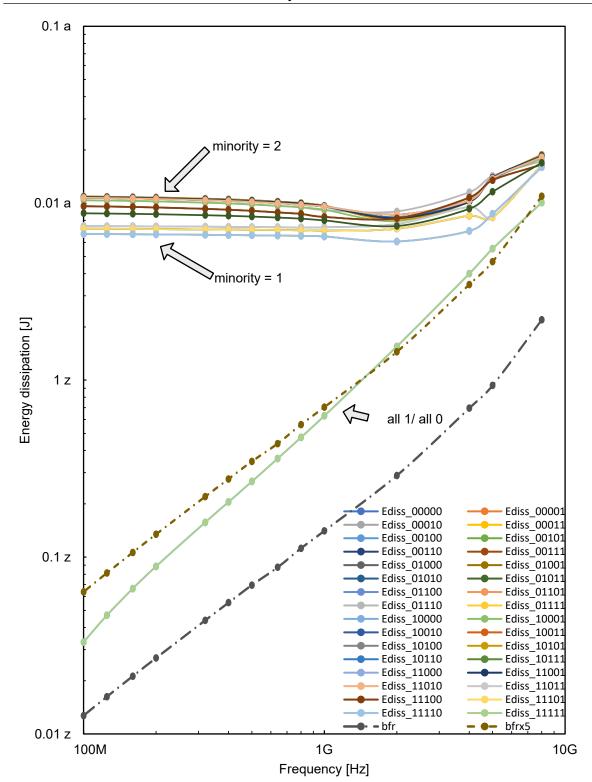

Figures 2.14 and 2.15 show the energy consumption of a 3-input majority logic gate and a 5-input majority logic gate.

Figure 2.14: The graph shows the frequency dependence of the power consumption of the AQFP 3-input majority gate. The three-input majority logic gate consists of three buffers, and when all inputs are equal ( $Ediss_{000}$ ,  $Ediss_{111}$ ), the energy consumed is approximately equal to the energy of the three buffers. In other cases, the operation is non-adiabatic and there is a lower bound on the energy consumption, which is approximately 0.01 aJ.

Figure 2.15: The graph shows the frequency dependence of the power consumption of the AQFP 5-input majority gate. A 5-input majority logic gate consists of five buffers, and when all inputs are equal ( $Ediss_{00000}$ ,  $Ediss_{11111}$ ), the energy consumed is approximately equal to the energy of five buffers. It also has two ranks of energy consumption when operating in a non-adiabatic manner, which is determined by the number of minority inputs, and the energy consumption when there are two minority inputs is greater. Minority = 1 and minority = 2 indicate the number of minority inputs.

#### 2.5.3 Design flow of AQFP circuit

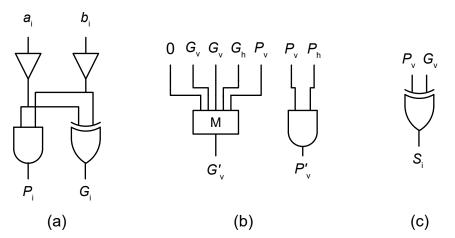

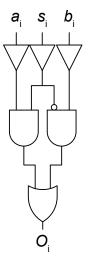

AQFP circuit basic cells and logic cells can be combined to create a circuit that operates. A 1-bit full adder is used as an example. The function for a full adder is shown in equations (2.23) and (2.24).

$$C_{\rm out} = ab + bc + ca \tag{2.23}$$

$$S = a \oplus b \oplus c \tag{2.24}$$

Logic synthesis

=

$$C_{\text{out}} = Maj(a, b, c) = ab + bc + ca \qquad (2.25)$$

$$S = Maj \left(\neg Maj \left(a, b, c\right), Maj \left(a, b, \neg c\right), c\right)$$

$$(2.26)$$

a, b denote the inputs, c denotes the lower bit carry input,  $C_{\text{out}}$  denotes the carry output, and S denotes the sum output.

First, consider what kind of logic gates are used to create a structure that satisfies the logical equation. Since the equation written in equations (2.23) and (2.24) is in disjunctive canonical form, we use methods [29, 30] to transform it into the following equation.

$$S = \begin{cases} \neg ab(a+b) = (\neg a + \neg b)(a+b) = a \oplus b & (c=0) \\ \neg (a+b) + ab = (\neg a \neg b) + ab & (c=1) \end{cases}$$

(2.27)

$$\neg c(a \oplus b) + c(\neg a \neg b) + ab = a \oplus b \oplus c \qquad (2.28)$$

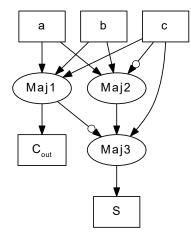

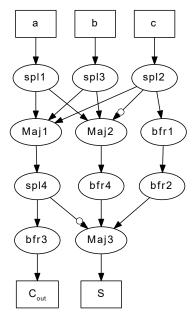

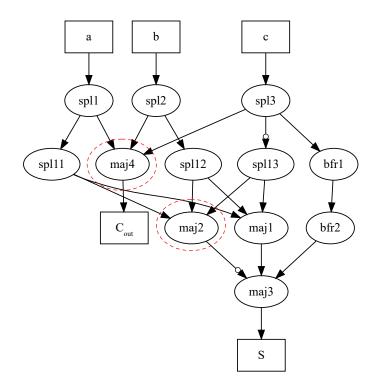

This logical equation equations (2.25) and (2.28) are expressed in terms of a network graph as shown in figure 2.16.

Figure 2.16: Network graph of full adder circuit by using majority logic gate. In this graph negative connection decreases as dot input.

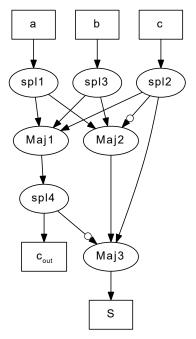

Since the branching of signals in the AQFP circuit requires branching gates (SPL2 and SPL3), the appropriate branching tree is connected below the logic gates. The network graph of the full adder after connecting the branch gates is shown in figure 2.17.

Figure 2.17: Circuit diagram of figure 2.16 with the split cells added.

Finally, a buffer is inserted to adjust the signal timing as shown in figure 2.18.

Figure 2.18: Network graph of the full adder, correctly designed as a logic circuit. Signal branch cells and buffer cells to adjust signal timing are inserted. This circuit is referred to as a type-A total adder for convenience.

We refer to this graph structure shown in figure 2.18 of full adder as type-A. It is a well-balanced structure in terms of energy consumed and latency. The graph shown in figure 2.19 is a type-B full adder, which has a shorter latency of  $C_{\rm out}$  than type-A. This feature is effective to design ripple carry adder. However, it consumes more energy than type-A due to a large number of branch cells and majority gates. As described above, even circuits with the same logic formulas have various characteristics, and it is very important to consider the implementation that suits the purpose.

Figure 2.19: Network graph of the full adder called type-B, has a shorter latency of  $C_{\rm out}$  than type-A. The two majority gates enclosed by the red dashed line perform the same operation.

# Chapter 3

# RTL to GDS flow for large AQFP circuits

#### 3.1 Introduction

In previous, various circuits have been designed and demonstrated using AQFP circuits. Examples of large-scale circuits include the 4-bit microprocessor MANA and the 16-bit Kogge-Stone adder[15, 31]. We designed these circuits mostly by hand, which required a long time to design. In particular, we spent much time verifying the designed layout. To use AQFP circuits in practical applications, even larger designs with more complexity are needed. The design environment must be improved to enable efficient circuit design.

There have been reports on the construction of semi-custom design flows for AQFP circuits[32] and methods for efficient placement of standard cell designs [33, 34, 35]. This chapter reports on the construction of a highly integrated full-custom design flow and a top-down design flow that outputs GDS from RTL in a fully automated manner, using Synopsys tools.

# 3.2 Full-custom environment setup and cell library development

#### 3.2.1 Full-custom setup

We have created an environment that allows designers to design custom AQFP circuits on a schematic layout editor known as Synopsys Custom Compiler. This tool is integrated with an analog/digital simulator and layout verification tool.

For analog simulation, PrimeSim HSPICE is used [36]. Compared to the previously used superconductor circuit analog simulators such as jsim[37], JoSIM[38], and WRSpice, it is a user-friendly simulator because it can use a variety of configurable voltage sources and can interactively set up simulation from the circuit design window [39]. It is also available to simulate circuits with sweeping parameters. This feature is convenient for checking the robustness of the designed circuit against fabrication parameter spread. Digital simulation is also available through PrimeSim XA (mixed signal mode) by invoking the System Verilog views developed for each AQFP logic cell.

We set up the layout versus schematic (LVS) on Custom Compiler for the layout verification tool. It is of great interest to circuit designers to know whether the circuit layout they have created correctly corresponds to a specified schematic. This checking is done carefully, but a minor design error can lead to a large failure[40]. LVS performs a mechanical comparison of the circuit layout and schematic, and plays a vital role in circuit design.

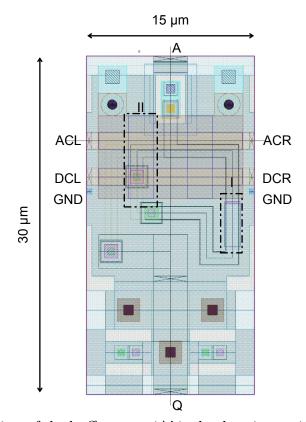

Our LVS tool currently supports checking the topology of graphs extracted from the schematic and layout. Figures 3.1 and 3.2 show the schematic and layout of the buffer gate of the AQFP, and LVS has verified the equivalence of these two. When the circuit is verified to be equivalent, the notification shown in listing 3.1 is obtained. LVS is available not only for the cell designed under the full-custom flow but also for larger circuits designed such as those built from the standard cell library. Inductor parameter checks are normally done via simple sheet inductance calculations which are not suitable for the complex multi-layer inductances that the AQFP has. Integration with a 3D solver such as STAR or InductEx [40] is necessary and will be in consideration in the future.

These developments have made designing AQFP circuits much more convenient than before. We used this environment to create cell libraries for the RTL-to-GDS flow of AQFP circuits.

Figure 3.1: Schematic of an AQFP circuit. $L_{in} = 1.67 \text{ pH}$ ,  $L_1 = L_2 = 1.42 \text{ pH}$ ,  $L_x = 5.19 \text{ pH}$ ,  $L_d = 5.17 \text{ pH}$ ,  $L_p = 8.39 \text{ pH}$ ,  $L_s = 30.9 \text{ pH}$ ,  $C_L = C_R = 2.90 \text{ fF}$ ,  $k_{x1} = k_{x2} = -0.22$ ,  $k_{d1} = k_{d2} = -0.14$ ,  $k_{tr} = 0.49$  and critical current of  $J_1$  and  $J_2$  are 50 µA. Parasitic couplings are ommitted in this figure.

Figure 3.2: Layout view of the buffer gate. 'A' is the data input, 'Q' is the data output, 'ACL' and 'ACR' are the left/right AC power-clock ports, and 'DCL' and 'DCR' are the left/right DC offset ports. The virtual GND lines for LVS in the standard cell design of the AQFP circuit are located below DCL and DCR. Blue rectangles in the dotted line box (I) and (II) are examples of using the inductance annotation layers for LVS. (I) indicates the primary inductor of the transformer and (II) indicates the individual inductance  $L_1$ .

#### 3.3 AQFP RTL-to-GDS flow

#### 3.3.1 Cell libarary development

We have designed a standard cell library for the MIT Lincoln Laboratory SFQ5ee process [41] for automated design flows. The critical current density of the Josephson junction (JJ) is  $100 \text{ A}/\mu\text{m}^2$ , and it has eight superconductor Nb layers available for circuit design [42]. The basic structure of the cell follows previous studies with some improvements to enable the previously mentioned verification flows [43].

We prepared two types of cells with the same function, one is an "odd" cell, and the other is an "even" cell, which is a mirrored image of the odd cell. The clocking of the AQFP circuit uses a method called 4-phase clocking[44], in which the DC bias current and two AC currents with phase differences of 90 degrees are wired in a meander pattern. Therefore, the DC bias currents flow from the left for cells excited by an odd numbered phase and from the right for cells excited by even numbered Listing 3.1: LVS execution log. It shows the results of comparing the netlist extracted from schematic and layout. The last line's "bfr == bfr" indicates that two netlists are matched.

```

Results Summary

_____

LVS Device Extraction Error Summary

2 total rules were run.

O rules NOT EXECUTED.

0 rules have violations.

There are 0 total violations.

Refer to bfr.LAYOUT errors

_____

LVS Compare Summary

LVS Compare Result: PASS

TOP equivalence point: [bfr,bfr]

equivalence points checked: 1

passed 1

failed 0

Refer to bfr.LVS_ERRORS for LVS Error Diagnostics

[PASS]

bfr == bfr

(level 0)

```

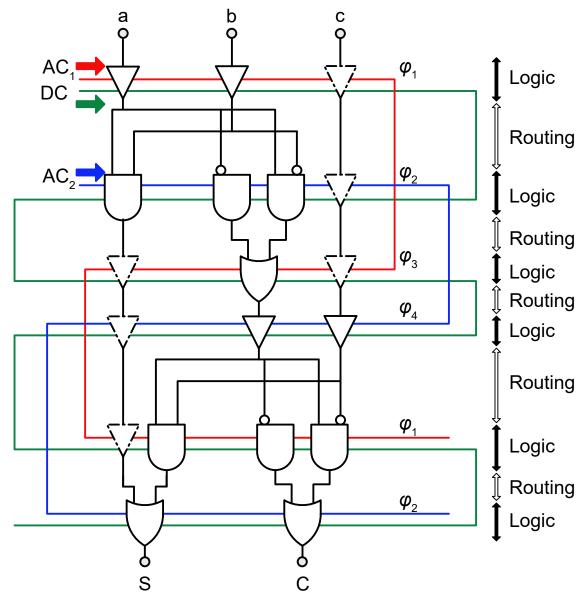

phases. Some gates, such as AND/OR gates, have a specific direction for DC bias currents due to the asymmetry of the AQFP circuit inductance in the constant cells needed to perform AND/OR. To treat this problem previously, the designer must manually turn the cell when they placed these gates in even-numbered positions. We decided to add the even cells that were initially flipped over to the standard cell library. Figure 3.3 shows AQFP AND/OR full adder circuit. Cells placed on  $\phi_2, \phi_4$ receive DC from right to left and thus "even" cells are chosen from the cell library for these phases. For  $\phi_1, \phi_3$ , "odd" cells are chosen. Making these odd/even cells explicitly available simplifies the modifications needed to obtain a correct placement.

AQFP circuits also have the problem of low circuit drive power, which is a major obstacle for long internal wiring and large branches/splitters. A circuit called a booster can solve this problem. Since it can reduce circuit latency and area. A four-branch cell using the booster and a long-distance wiring cell are included in the cell library. Further, cells are individually characterized to identify the maximum interconnect length they can drive. This information is included in a Liberty file that describes the driving strength of each cell for use in the top-down design flow.

The larger the circuit, the more the effect of signal delay time needs to be considered. Since AQFP circuits have logic gates connected in a daisy chain to the clock (excitation current), attention must be paid to the clock delay time. The wiring which provides the excitation current is changed from a simple inductor model to an LC ladder model [45]. The excitation current overlaps the inductance of the SQUID part of the AQFP circuit. Therefore, there are both magnetic, and capacitive coupling effects. It is now possible to evaluate the excitation timing discrepancy due to the propagation delay of the excitation current.

Figure 3.3: Schematic of AQFP AND/OR full adder. Two AC lines and one DC line are wired in a meander shape like this figure. The region of routing and logic cells are placed alternately. The buffer gate depicted by the dashed line is inserted during the path-balancing process. "Even" cells are used which belong to  $\phi_2, \phi_4$ .

Figure 3.4: Two files are prepared: a Makefile and an HDL file describing the circuit to be designed. The Makefile contains the binary path and the module name, and the top-down flow begins by executing the Makefile with the "make" command.

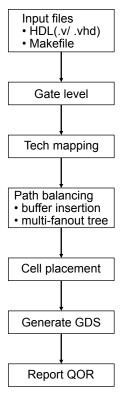

#### 3.3.2 AQFP RTL-to-GDS flow

Cell placement and routing are done within Synopsys's framework of the Fusion Compiler system. The tool set is highly customizable through TCL scripting, with a very flexible and complete interface to the design database. Our AQFP flow consists of a master script, which calls subsidiary scripts to perform the various tasks, from library compilation through synthesis, formality checking, place and route, and documentation. Figure 3.4 shows a rough flowchart of this top-down flow.

Initially, technology mapping to the AQFP library is performed. Synthesis uses abstract cells that avoid issues particular to AQFP, such as using a multi-phase clock, so mapping to the "real" library cells is required. Once mapped, the next operation is path balancing, ensuring that the combinational cells' inputs originate from the same logic depth within a pipeline. This process involves adding AQFP buffer cells into the design, generally in large numbers. As a by-product, all combinational cells are assigned a logic level number, starting from one at the beginning of each pipeline state.

A floor plan for the design is generated from the per-level gate counts and externallyset variables. This assembles the cell placements into rows, where each logic level has a corresponding cell row, starting from the top. A fixed-height wiring channel separates the rows. As a consequence of path balancing, all routes will connect adjacent rows, like figure 3.3. Cell placement and routing are usually done within this floor plan, minimizing a cost function that depends heavily on the total wire length. The routing flow is timing dependent and can compensate for timing errors by adding buffering or adjusting path length. Our flow uses four physical routing layers and horizontal and vertical strip passive transmission lines. These lines have a known delay proportional to distance. Clock delay is obtained from cell clock terminal placement, as the clocking routes are predictable from the floor plan. Again, the delay is proportional to the distance along the clock lines from a reference point.

Once placement and routing are complete, the GDS layout file and a QoR report are generated. The report identifies possible DRC errors and timing violations. In a typical design, there are often congestion points where routing effectively fails.

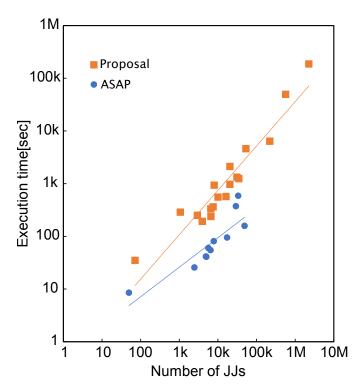

#### 3.3.3 Quality of result

Implementation results are shown in table 3.1 and figure 3.5. In the appendix, there are raw data to make this table. We compiled a set of ISCAS-85 benchmarks [46] and multi-bit adders to compare with a previous study, ASAP [33]. Among the ISCAS-85 benchmarks, the C6288 circuit (a  $16 \times 16$  array multiplier comprising half-adders and full-adders) yielded the largest JJ count at over 220k JJs. To investigate the scaling limitations of the tool, we included a simple, parameterized multi-bit adder with data word sizes ranging from 8-bit to 1024-bit. The comparison results are not completely fair because of the different cell libraries and different hardware used to compute the results, but nonetheless we can gain some insight into the differences between the approaches. Clearly, ASAP is superior in terms of execution speed. The overall JJ usage (fewer JJs is better) is also superior in ASAP as its usage is slightly better for some benchmarks, and much better in others, particularly the C6288 benchmark. One explanation for this is that ASAP was built from the ground up to support AQFP logic specifically. The RTL-to-GDS flow in this study still uses algorithms made for semiconductor circuits but with customized tool control via TCL scripting. For example, ASAP has a more proper treatment of AQFP buffer insertion and optimization (retiming). While buffer insertion is implemented in this study, it was not optimized to the extent ASAP was. Given that buffering can contribute to more than 90% of the JJs of an AQFP circuit [32], the lack of extensive buffering optimization can explain why the JJ usage is higher in this study.

However, our tool has successfully synthesized much larger circuits than ASAP. It consistently demonstrated its capability to realize designs in the range of 100k JJs to over one million JJs. The largest circuit successfully designed is a 1024-bit adder with two million JJs. The design took two days on a server with 1024 GB of memory in the cloud. Further, the internals of the RTL-to-GDS engine is shared between RSFQ and AQFP logic. The only difference is the customization of the flow through scripting. ASAP only supports AQFP logic. Lastly, the top-down design flow is well-integrated with the full-custom flow which provides a seamless user experience compared to the standalone flow available via ASAP.

|                | Prop    | oosal    | A     | SAP      |

|----------------|---------|----------|-------|----------|

| name           | #JJs    | time (s) | #JJs  | time (s) |

| C17            | 72      | 35       | 50    | 9        |

| C432           | 3958    | 193      | 2474  | 26       |

| C499           | 6656    | 238      | 5046  | 41       |

| C880           | 7546    | 363      | 6480  | 55       |

| C1355          | 6584    | 333      | 4918  | 42       |

| C1908          | 10112   | 557      | 5680  | 60       |

| C2670          | 16258   | 570      | 7884  | 81       |

| C3540          | 20520   | 973      | 17420 | 95       |

| C5315          | 31352   | 1326     | 29454 | 374      |

| C6288          | 220428  | 6383     | 49394 | 158      |

| C7552          | 35066   | 1246     | 33530 | 591      |

| 8-bit adder    | 1072    | 288      |       |          |

| 16-bit adder   | 2966    | 252      |       |          |

| 32-bit adder   | 8028    | 936      |       |          |

| 64-bit adder   | 20636   | 2124     |       |          |

| 128-bit adder  | 53290   | 4608     |       |          |

| 512-bit adder  | 567616  | 49536    |       |          |

| 1024-bit adder | 2275472 | 187200   |       |          |

Table 3.1: Comparison of placement results between ASAP[33] and proposal.

Figure 3.5: Graph of the number of Josephson junctions(JJs) vs. execution time. ASAP in the previous study is superior in both execution time and scalability. However, our method successfully designs circuits with larger JJs.

## 3.3.4 Discussion

During this study, the following was elucidated in regard to the characteristics of AQFP circuits compared to the conventional RSFQ circuits from perspective of RTL-to-GDS challenges.

In AQFP logic, the gates that make up the architectural latches are also clocked by the global excitation current [47]. These latches are composed of multiple cells and thus require multiple clock phases. It is difficult to resolve the timing of the combinational logic with architectural latch macros composed of multiple gates, so sequential circuits cannot be automatically synthesized at this moment. The quantum-flux-parametron latch (QFPL) is an AQFP-compatible latch without a feedback path, but it requires an additional control line [48] and still requires additional logic gates to interface with it. In addition, there have not been many reports of sequential circuit design using AQFP circuits. Methodologies have been proposed in [49, 50], but it still remains unclear how to properly automate the physical placement of the architectural latches together with the combinational logic, which all can influence the spacing between logic rows and apply even more interconnect constraints on a heavily constrained problem (interconnect length limitation).

In comparison, RSFQ logic has a high degree of freedom with the clock, making it easy to design complex circuits and cells with internal states. However, the overall number of JJs in the circuit increases because of the need for active JJ circuits to distribute the clock. Also, RSFQ logic tends to have more JJs per cell compared to AQFP logic [51]. Thus, synthesis flows for RSFQ logic can more easily approach higher JJ counts for the above reasons, especially because the lower cell count (with more JJs per cell) reduces the computation/memory load for the RTL-to-GDS flow when compared to AQFP logic.

AQFP physical synthesis is hindered by a more heavily constrained placement flow as cells cannot be placed on any arbitrary row, but only on a row that provides the required clock phase it needs to be excited by. For example, an AQFP cell that must be excited by  $\phi_2$  must be placed only on  $\phi_2$  equivalent rows in 4-phase clocking. This constrains the placement of the cell to just 25% of the rows available for a given circuit design which may be challenging for a placer to find a good solution.

RSFQ circuits allow transmission over long distances using passive transmission lines (PTLs)[52]. AQFP circuits use buffers as repeaters to transmit across long distances, which increases latency and creates more constraints on the place-androute solution because the repeaters themselves also require a power-clock. This can be partially mitigated by the aforementioned boosters in Section 3.2. Another approach is to convert the AQFP signal to SFQ pulses to enable ballistic propagation using PTLs. However, the energy consumption of the RSFQ circuit to support this is 1000 times higher than that of the AQFP circuit, limiting its adaptability[53]. An intensive trade-off analysis needs to be conducted to determine what is the most suitable strategy.

Fewer JJs are required to perform arithmetic operations in AQFP logic. This is because it intrinsically uses majority logic as the basis of logic computation. Majority logic has been shown to be much more efficient for arithmetic [54, 29]. That is not to say that RSFQ logic cannot do majority logic, but the implementation of a 3-input majority gate (MAJ3) in RSFQ logic requires 23 JJs [55], while the MAJ3 in AQFP logic requires only 6 JJs [26].

## 3.4 Conclusion

We developed full-custom and top-down design flows using Synopsys EDA tools for AQFP circuits. The full-custom flow is integrated with simulation and verification tools such as analog/digital simulators and LVS. This provides an improved design efficiency and user experience.

The top-down flow is the first attempt to build a tool that fully automates the design from RTL to physical information that can be taped out. This is the first successful design of AQFP circuits exceeding millions of JJs.

The next steps for this work include the following: (1) enable circuit parameter verification of complex inductor structures by integrating 3D solvers into the LVS flow, (2) provide an easy way to adjust optimization constraints such as relaxing interconnect constraints or area constraints, and (3) provide support for novel clocking methodologies such as power-divider clocking [56] and delay-line clocking [57] as they may provide substantial opportunities to reduce latency and buffering [25, 58].

# Chapter 4 Channel routing for AQFP circuits

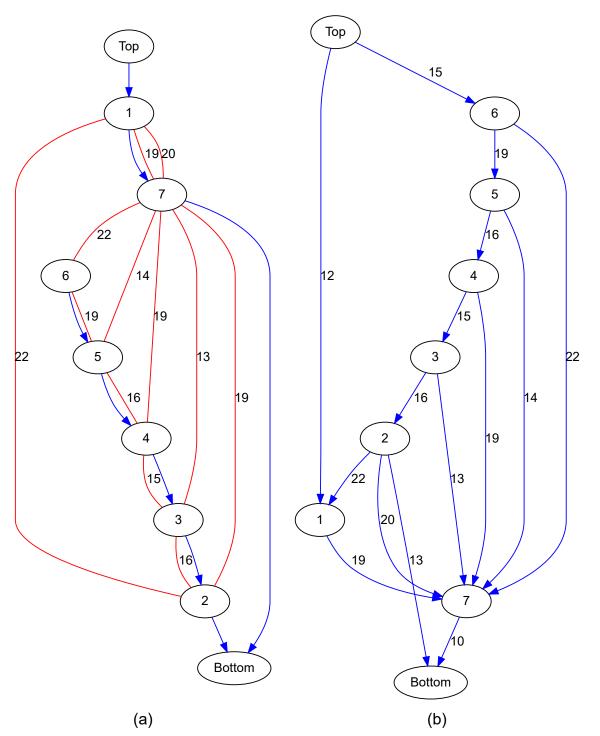

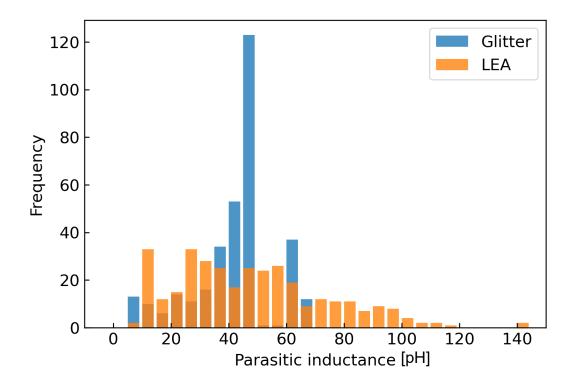

This chapter describes the left edge algorithm, which is widely used in AQFP circuits, and the Glitter routing algorithm used when the routing width is not constant. Then, the Glitter-based routing inductance optimization algorithm is described and the results of its execution are discussed.

# 4.1 Routing structure of AQFP cirucits

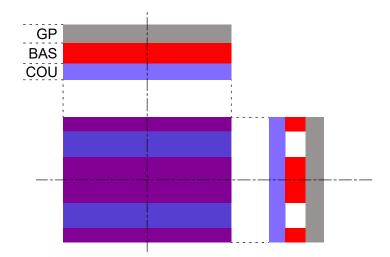

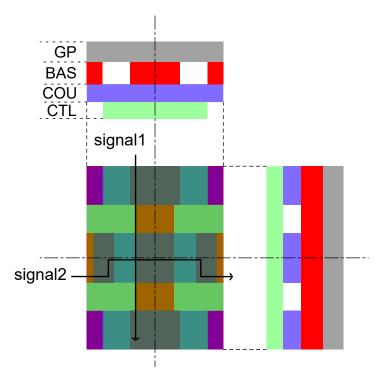

The HSTP process has four metal layers (layers made of Nb): GP, BAS, COU, and CTL. The strip line structure is a structure in which a ground surrounds the top and bottom of the line through which the signals pass, and the GP layer covers the signal wire as the bottom ground and the COU layer for the top ground. Figure 4.1 shows the layer structure of the stripline at the HSTP process. Figure 4.2 shows the cross-section of signal lines. The CTL layer covers the signal wire as the upper ground, and the BAS and COU layers are used to cross the signals. Therefore, only two layers are available for signal routing.

The channel routing algorithm for AQFP circuits uses the most popular left-edge method[59].

Figure 4.1: AQFP wiring stripline structure. The signal current passes through the BAS layer, with the COU and GP layers covering the top and bottom of the BAS layer. On the sides of the signal lines, the BAS layer wired along the signals connects the top and bottom grounds.

Figure 4.2: Diagram of a cross-section of signal lines in an AQFP circuit. The CTL layer covers the upper side, and the GP layer covers the lower side to protect the signal lines of the BAS and COU layers that cross.

## 4.1.1 Left edge algorithm

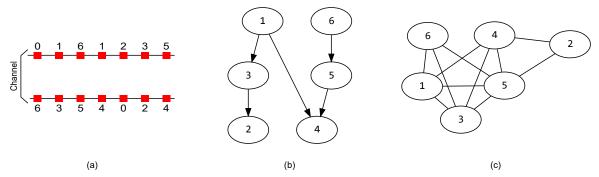

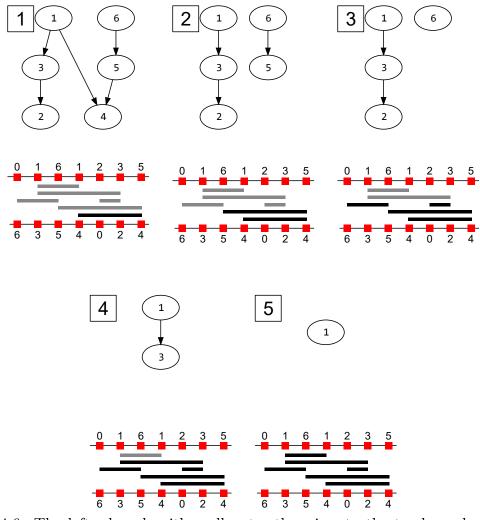

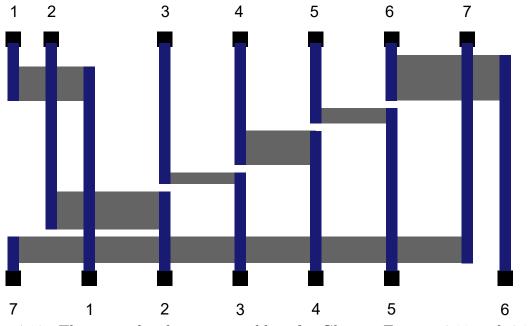

Left edge algorithm(LEA)[60, 61] is so named because it scans the signal edge from the left edge of the routing area and assigns the track (horizontal routing grid in the channel area) that the wires use. The algorithm creates two graphs from the state of the channel region and processes the graphs to perform the routing. figure 4.3 (a) shows an example of a wiring region.

Figure 4.3: (a) Example of the channel area. Numbers indicate the connection relationship of each terminal. 0 indicates no terminal. (b) VCG created from Figure (a). (c) HCG created from Figure (a).

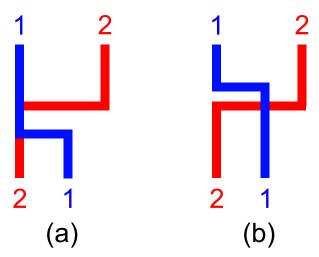

#### Vertical Constrain Graph

A vertical constrain graph (VCG) is a directed graph for determining the order in which to route. The VCG corresponding to (a) in figure 4.3 is (b). The left edge algorithm has the possibility of incorrect routing depending on the order of track assignment. For example, as shown in figure 4.4 (a), if signal lines '1' and '2' are placed in order from the bottom, there will be no vertical wiring area for signal line '2. This mistake can be solved by wiring signal line '2' first, as in figure 4.4 (b). The wiring order is specified in this situation by adding the edge '1' to '2' to the VGC. Wiring can be done without overlap by sequentially wiring from the signal line corresponding to the node of the leaf of the final created VCG. In the case of Figure 4.3(b), wiring '2' is permanently wired before wiring '1'. In addition, since wiring '2' and '4' have no relationship in VCG, there is no restriction on the wiring order.

Figure 4.4: Cases where wiring must be constrained using VCG. In case (a), the vertical wiring on the left side is crossed, but this is eliminated in state (b). Changing the order of the horizontal wiring can control the crossing wires.

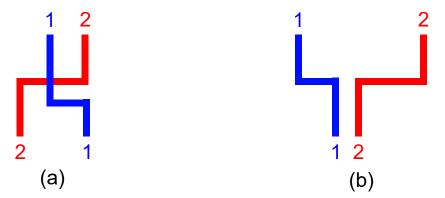

#### Horizontal Constrain Graph

The horizontal constrain graph (HCG) is an undirected graph describing the possibility of horizontal wiring overlap. figure 4.3 (c) is the HCG generated from (a). If two nodes of the HCG are adjacent to each other, the signal lines corresponding to those nodes cannot be routed on the same track. In figure 4.5 (a), node '1' and node '2' are connected, and in (b), there is no edge between node '1' and node '2'. In other words, in (b), wires '1' and '2' can be placed on the same track.

Figure 4.5: (a) has a relationship in the HCG, while (b) does not. In (a), assigning horizontal signal lines to the same track causes overlap, while in (b), this does not occur.

Algorithm flow of left edge algorithm Algorithm 4.1 shows pseudocode of LEA.

#### Algorithm 4.1 Left edge algorithm

#### 1: repeat

- 2: node-set  $\leftarrow$  set of leaves in VCG

- 3: wires  $\leftarrow$  set of node-set where wire not connected in HCG

- 4: Putting wires

- 5: Delete wires from HCG and VCG

- 6: until HCG and VCG are empty

Figure 4.6: The left edge algorithm allocates the wires to the track, and when the VCG is empty, it means that the wire allocation has been completed.

There is a restriction in this algorithm that wiring cannot be performed unless the VCG is a directed acyclic graph (DAG). This means that even if the order of wiring placement is changed, there exists a situation where vertically oriented signal lines overlap as shown in figure 4.7. It is necessary to arrange the logic cells in such a way

that this constraint is satisfied.

Figure 4.7: Wiring example when VCG is not a DAG. (a) If such a combination of terminals is present in the circuit, the wiring will fail if the signal line bends only twice. Therefore, adding a structure called DOGLEG, which wires by bending four times. (b) The VCG generated from (a) has no leaves and cannot be wired because of the circulation.

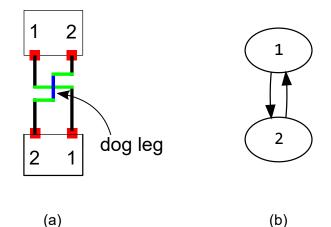

In the AQFP circuit, the upper and lower cells are positioned at different positions, as shown in figure 4.8, to prevent the VCG from becoming a cyclic graph. The I/O pin spacing of the AQFP circuit is  $20 \,\mu\text{m}$ , and the width of the signal lines is  $10 \,\mu\text{m}$ , including the shield. By shifting the placement of the upper and lower cells by  $10 \,\mu\text{m}$ , the vertical wiring of the upper and lower cells will not collide, which can be attributed to the wiring problem of no VCGs, and the left edge algorithm can always be used for wiring.

Figure 4.8: The method to avoid making cycle in VCG of AQFP circuit routing problem. By shifting the placement of the upper and lower cells by  $10 \,\mu\text{m}$ , the vertical wiring of the upper and lower cells will not collide.

## 4.2 Channel routing optimization with Glitter

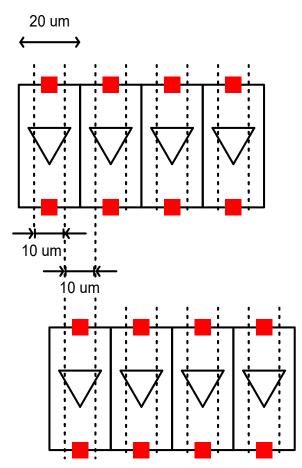

A stripline connects the AQFP gate and gate, and the strip line is part of the superconducting loop. Since the flowing current in the superconducting loop is inversely proportional to the inductance of the loop, the current flowing in the long strip line is small. The minimum sensitivity of the AQFP circuit designed for the HSTP process is about 7 µm, which is the current that flows when the parasitic inductance is 50 pH. If the inductance is higher than this, arithmetic errors due to thermal noise will occur frequently, so this is a rule that must be followed in the design. Where  $\mu_0$ is permeability in vacuum, w is width of signal wire,  $d_n$  is ditstance between signal wire to ground plane, and  $\lambda_n$  is London penetration depth.

$$L_n = \mu_0 \frac{\left(d_n + 2\lambda_L\right)l}{w} \tag{4.1}$$

As can be seen from equation (4.1), the parasitic inductance is inversely proportional to the width. If the wiring width is wider, the inductance per length can be reduced, which means that more extended wiring is possible.

Figure 4.9: Parasitic inductance per  $100 \,\mu\text{m}$  vs wire width. Inductance can be small when wider wire is used.

The figure shows the relationship between wiring width and inductance per length and between wiring width and maximum wiring length. 3 mm wiring is possible if 30 µm width wiring is used.

## 4.3 Glitter, variable-width channel router

Using wide signal lines can increase the data transmission distance, but it also increases the area of the circuit. If wide wiring can be used for long-distance signal lines and thin wiring for short distances, data can be propagated over long distances without increasing the circuit area. This technique can be achieved using Glitter[62], an algorithm that enables correct wiring in wiring areas where the wiring width is not constant.

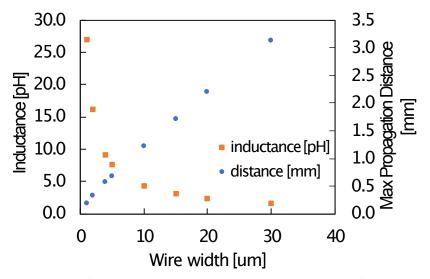

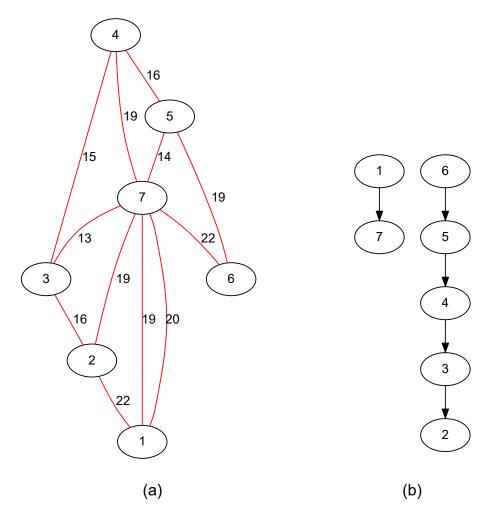

## 4.3.1 Routing Algorithm

In this section, the Glitter algorithm is briefly explained. Glitter is an algorithm that is an extension of the left edge algorithm and generates a weighted constrain graph (WCG) by generating a weighted VCG and HCG and combining them. Figure 4.11 shows HCG and VCG corresponding to figure 4.10, and figure 4.12 shows WCG from figures 4.10 and 4.11. Since the generated WCG is a graph with a mixture of undirected and directed edges, the orientation of the undirected edges is calculated according to the algorithm to convert the WCG to a DAG. The direction is given such that the channel area is minimized.

Figure 4.10: The example of routing problem for Glitter. Figures 4.11 and 4.12 is generated from this problem.

Figure 4.11: (a) HCG of routing problem of figure 4.10. (b) VGC of routing problem offigure 4.10.

Figure 4.12: (a) Initial state of weighted constrain graph. This graph is generated by merging HCG and VCG of figure 4.11. (b) Final state for WCG. This is DAG. The wire is assigned from the edge with the smallest maximum weight from the top and bottom.

## 4.3.2 Flow to decide the width of wire

The algorithm for determining the wiring width is described below. The implementation is simple, since previous experimental results have shown that a simple algorithm is sufficient.

Repeat the four steps as shown below to reduce the inductance of the wiring in the channel to 50 pH or less.

- 1. Determine the required wiring width from the wiring length.

- 2. Using the Glitter algorithm, determine the wiring sequence. This determines the channel width.

- 3. Update the channel width. Recalculate the inductance of the wiring.

- 4. Check if all inductances in the channel are below the target value (50 pH). If confirmed, exit the program; otherwise, return to step 1.

When this algorithm is executed, wiring with shorter distances in the channel becomes thinner, and wiring with longer distances becomes wider than the standard width of AQFP wire. Since the channel length is the sum of the widths of each wire, as the number of thicker wires increases, the channel length also increases. The increase in channel length may cause positive feedback because the wires are incentivized to be thicker. Therefore, thicker wiring in the initial conditions can prevent positive feedback.

## 4.3.3 Test result

The proposed method was applied to a circuit with about 400 wires, and the results obtained are shown in table 4.1.

|          | LEA               |           | Glitter           |           |  |

|----------|-------------------|-----------|-------------------|-----------|--|

| #channel | Max inductance pH | # buffers | Max inductance pH | # buffers |  |

| 1        | 81.8              | 44        | 46.6              | 0         |  |

| 2        | 77.4              | 40        | 43.6              | 0         |  |

| 3        | 94.6              | 48        | 41.1              | 0         |  |

| 4        | 82.4              | 42        | 48                | 0         |  |

| 5        | 151               | 174       | 71.9              | 58        |  |

| 6        | 110.1             | 78        | 48.5              | 0         |  |

| 7        | 97.3              | 26        | 47.5              | 0         |  |

| 8        | 79.8              | 18        | 46.7              | 0         |  |

| 9        | 78.3              | 10        | 47.5              | 0         |  |

| 10       | 67.8              | 8         | 46.4              | 0         |  |

| 11       | 41.2              | 0         | 41.2              | 0         |  |

| Total    |                   | 488       |                   | 58        |  |

Table 4.1: Test result of inductance optimization by using Glitter channel router.

Figure 4.13: Hisgram of parasitic inductance of wire in the benchmark circuits. With the optimization, peaks are visible at less than the threshold value of 50 pH in Glitter, whereas the values were scattered in LEA.

## 4.4 Conclusion

In this chapter, the routing method of the AQFP circuit is described. First, the wiring structure in the HSTP process and the left edge algorithm, which is the basic algorithm, are described.

There is a strict limit to the wiring distance in AQFP circuits, and this limit is due to the parasitic inductance of the interconnections, which can be extended by using interconnections with low inductance per unit length, i.e., wide interconnections. However, increasing the wiring width leads to an increase in the circuit area, so the wiring algorithm using Glitter that flexibly determines the wiring width is proposed.

As the clock frequency increases, the AQFP gate and the characteristic impedance difference between the wiring and the AQFP gate may reflect due to the difference in impedance[63], which may interfere with signal propagation. Therefore, it is necessary to design wiring that includes a stripline filter and to calculate in advance combinations of wiring widths and distances that cannot be used.

# Chapter 5 Ciruit design and test

In this chapter, the actual circuits designed will be discussed.

## 5.1 Adder(Kogge-Stone adder)

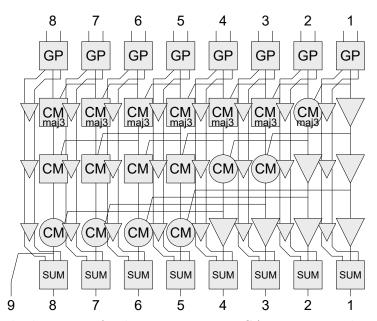

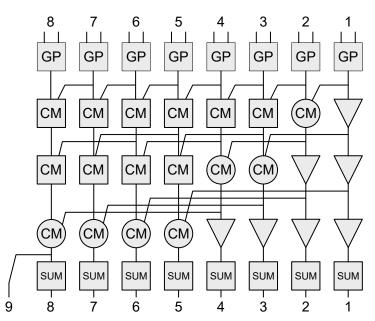

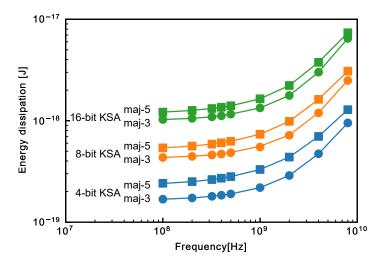

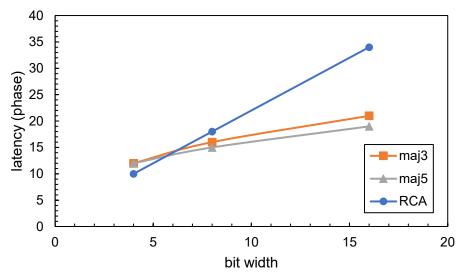

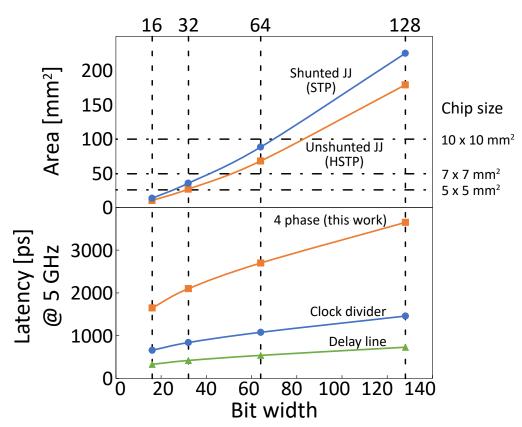

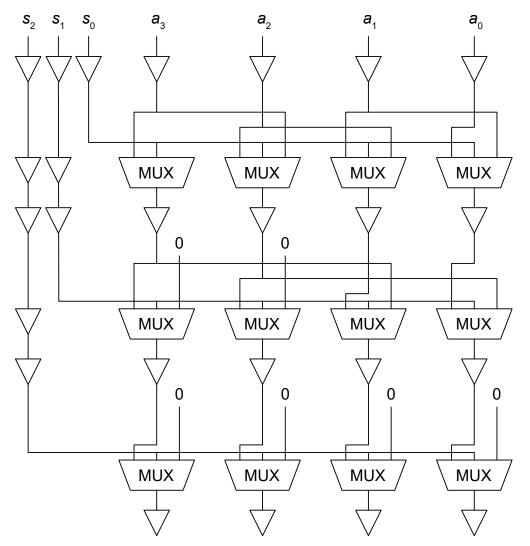

The 16-bit majority-3 KSA and the 8-bit majority-5 KSA were designed and demonstrated in operation. In addition, 4-, 8-, and 16-bit majority-3 and majority-5 KSAs were designed to evaluate their performance in simulation, and a comparison of their performance is also reported.

The adder is the fundamental operation in logic operations. The performance improvement of the adders has a significant impact on the entire system.

## 5.1.1 Architecture

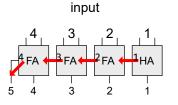

There are various adder architectures, including ripple carry adder (RCA), Carry Save Adder (CSA), carry-lookahead adder(CLA), and carry prefix adder (CPA). The CSA and CLA are speed-up techniques for RCA and CPA. Figure 1 shows the architecture of RCA. (a) is a block diagram of the implementation method in CMOS circuits and RSFQ, and (b) is a block diagram of the implementation method in AQFP circuits. The RCA has a structure connecting all full adders' carry signals in sequence. The AQFP circuit cannot perform asynchronous operations, so data must be stored in first-in-first-out memory using buffer gates until the carry signal arrives. Since a large FIFO is required, the area and JJs are inefficient. When RCAs are implemented in an AQFP circuit, the latency is O(N), and the JJs is  $O(N^2)$ .

CPA is known as a faster adder than RCA. The following is an overview of how CPA works. Let the two n-bit operands be denoted as  $A = (a_{n-1}, a_{n-2}, ..., a_0)$  and  $B = (b_{n-1}, b_{n-2}, ..., b_0)$  and the sum of A and B as  $S = (s_n, s_{n-1}, ..., s_0)$ . And to introduce intermediate answer  $p_i, g_i$  and it is defined as

$$g_i = a_i \times b_i$$

$$p_i = a_i \oplus b_i$$

(5.1)

$g_i$  equal to "1" indicates carry generates from i-th bit.  $p_i$  equal to "1" indicate carry generates if  $g_{i-1}$  equal to "1". And also, an operator "o" is introduced which

output (a) Block diagram of RCA in CMOS and RSFQ circuits.

output

(b) Block diagram of RCA in AQFP circuit. A lot of buffer gates (FIFO memory) are needed, which were not shown in (a).

works as following equations.

$$(g,p)o(g',p') = (g+g'p',pp')$$

(5.2)

This operation works for contentious sequences bit i to bit j and  $(g_{i:j}, p_{i:j})$  indicate the result of operation "o" from i to j.

$$(g_{i:j}, p_{i:j}) = (g_i, p_i)o(g_{i-1}, p_{i-1})o...o(g_{j+1}, p_{j+1})o(g_j, p_j)$$

(5.3)

It is continuance "o" is also adaptable for  $(g_{i:j}, p_{i:j})$ .

$$(g_{i:k}, p_{i:k}) = (g_{i:j}, p_{i:j})o(g_{j-1:k}, p_{j-1:k})$$

(5.4)

$g_{i-1:0}$  indicates carry will arrive bit-*i* th and finally result of addition can be derived by

$$s_i = g_{i-1:0} \oplus p_i \tag{5.5}$$

Finally, the summation result S can be derived by

$$S = (s_n, s_{n-1} \cdots s_1, s_0) = (g_n, g_{n-1:0} \oplus p_n, g_{n-2:0} \oplus p_{n-1}, g_{1:0} \oplus p_1, p_0)$$

(5.6)

By setting j to j = (i + k)/2 in equation (5.4), the computation of  $g_{i:j}$  and  $p_{i:j}$  can be represented by a binary tree. Therefore, the computation time of this adder is  $O(log_2N)$ , which is much faster than CSA.

There are many variations of the CSA, which differ in the number of fanouts, the number of wire lengths, and the number of logic gates used. AQFP circuits are suitable for adders with the Kogge-Stone structure, which are CSAs with fewer fanouts because of the low gate driving power.

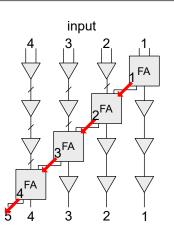

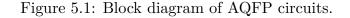

figures 5.2 and 5.7 shows block diagram of majority-3 based and majority-5 based KSAs, respectively. There is a small difference in architecture, but the algorithm is the same.

Figure 5.2: Block diagram of 8-bit majority-3 KSA. Logic inside of the circuit is shown in figure 5.3. To deduce latency, the SUM stage uses  $g_i, p_i$ , and a buffer chain is required to propagate these signals.

Figure 5.3: Inside of block diagram of majority-3 KSA. (a) GP block. (b)CM maj-3 block. (c) Standard CM block. (d) SUM block.

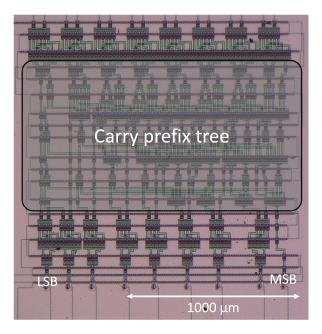

### 5.1.2 16-bit majority-3 based KSA

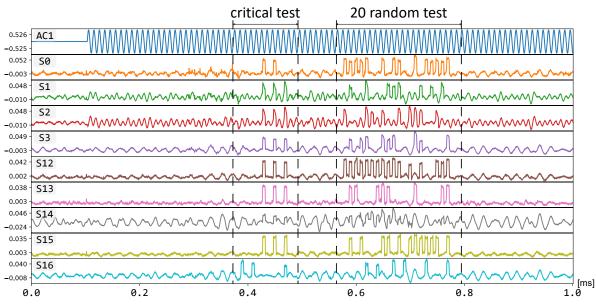

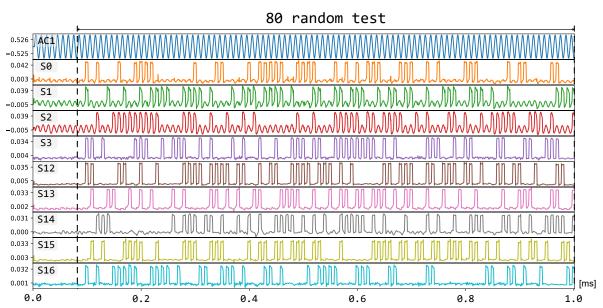

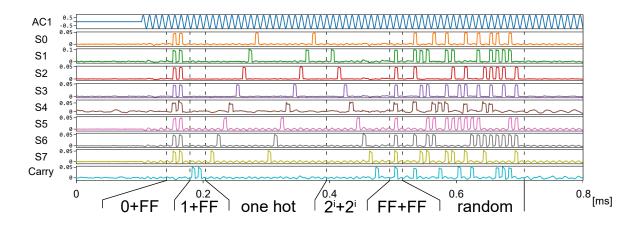

Figure 5.4 shows microphotograph of majority-3 based KSA. And, the circuit parameters are shown in the table 5.1. Figures 5.5 and 5.6 show measurement result.

We tried two sets of tests: critical tests and random tests. The critical tests were five test vectors that we explicitly defined to demonstrate pass-through of propagate signals, generation of carry from every bit, and full-propagation along the carry chain from the least significant bit (LSB) to the most significant bit (MSB). If the carry output is correct in the latter case, it is a very a good indication that the prefix signals are properly propagating along the long interconnects between stages, and that the carry prefix tree is working properly. Table 5.2 lists the critical test vectors we applied and the expected result. We then proceeded to apply a set of random vectors for a total of 110 random additions, as shown in Table 5.3.

figure 5.5 shows the results of the critical tests and 20 random tests, and figure 5.6 shows the results of 90 additional random tests at 100 kHz. The dc-SQUID-based output interface of the KSA produces a unipolar return-to-zero signal. When the output is a logic '1', the output signal rises and then falls back to zero proportional to the applied clock period of the AC clock. When the output is a logic '0', the output signal remains low. We confirmed that both the critical tests and the random tests passed. Even though our experiment was not fully exhaustive, these successful tests provide a strong indication that our design is working correctly.

Some of the outputs were rather noisy with S14, in particular, being very unstable. We attribute this to the measurement equipment condition at the time of this writing. Furthermore, we measured the operating margins of the circuit by adjusting how much we can change the amplitudes of AC1 and AC2 before the circuit malfunctions. The operating range is -4.29 dBm to 0.90 dBm for AC1, and -3.41 dBm to 1.02 dBm for AC2. Both ranges are sufficiently wide.

| X mm          | 2.8  |

|---------------|------|

| Y mm          | 3.6  |

| Latency cycle | 8.5  |

| JJs           | 4976 |

Table 5.1: Specification of majority-3 based KSA

Figure 5.4: Microphoto graph of 16-bit majority-3 based KSA.

Figure 5.5: Measurement waveform of the 16-bit KSA for 5 critical test vectors shown in Table 5.2 and the first 20 random test vectors shown in Table 5.3. The signals from top to bottom are the excitation current, output bits 0 (LSB) to 3, bits 12-to-15, and the output of the carry (MSB). Critical tests include test cases in which the carry moves from the LSB to the MSB. All tests cases have been validated.

Figure 5.6: Measurement waveform of the 16-bit KSA showing 90 random test vectors listed as 21 through 110 in Table 5.3. The signals from top to bottom are the excitation current, output bits 0 (LSB) to 3, bits 12 to 15, and the output of the carry (MSB). All observable outputs have been validated. The waveform traces have been averaged to show a clearer picture.

Table 5.2: List of critical test vectors applied in experiment.

| Op. A  | Op. B  | Result  | Description                      |

|--------|--------|---------|----------------------------------|

| OxFFFF | 0x0001 | 0x10000 | Propagate carry through all bits |

| 0x0001 | OxFFFF | 0x10000 | Propagate carry through all bits |

| OxFFFF | 0x0000 | OxOFFFF | Operand A passthrough            |

| 0x0000 | OxFFFF | OxOFFFF | Operand B passthrough            |

| OxFFFF | OxFFFF | Ox1FFFE | Generate carry at all bits       |

|                      | Op. A                                                                                       | Op. B              | Result             | -44             | Op. A              | Op. B              | Result  |

|----------------------|---------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------|--------------------|--------------------|---------|

| _#                   | 0x00E4A                                                                                     | 0x0075B            |                    | #               | 0x06C45            |                    |         |

| 1                    |                                                                                             |                    | 0x015A5            | 56 - 56         |                    | 0x068A6            | 0x0D4EB |